Micrel

SY100E151(1998) データシート - Micrel

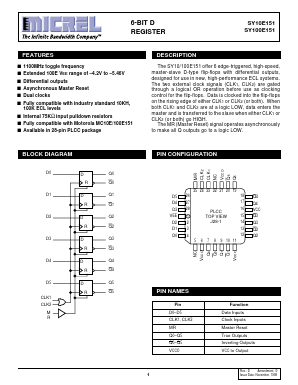

DESCRIPTION

The SY10/100E151 offer 6 edge-triggered, high-speed, master-slave D-type flip-flops with differential outputs, designed for use in new, high-performance ECL systems. The two external clock signals (CLK1, CLK2) are gated through a logical OR operation before use as clocking control for the flip-flops. Data is clocked into the flip-flops on the rising edge of either CLK1 or CLK2 (or both). When both CLK1 and CLK2 are at a logic LOW, data enters the master and is transferred to the slave when either CLK1 or CLK2 (or both) go HIGH.

The MR (Master Reset) signal operates asynchronously to make all Q outputs go to a logic LOW.

FEATURES

■ 1100MHz toggle frequency

■ Extended 100E VEE range of –4.2V to –5.46V

■ Differential outputs

■ Asynchronous Master Reset

■ Dual clocks

■ Fully compatible with industry standard 10KH, 100K ECL levels

■ Internal 75KΩ input pulldown resistors

■ Fully compatible with Motorola MC10E/100E151

■ Available in 28-pin PLCC package