Renesas Electronics

RD74LVC16374BTEL データシート - Renesas Electronics

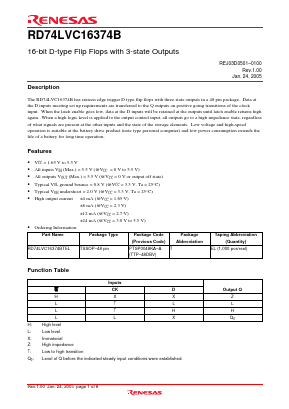

Description

The RD74LVC16374B has sixteen edge trigger D type flip flops with three state outputs in a 48 pin package. Data at the D inputs meeting set up requirements are transferred to the Q outputs on positive going transitions of the clock input. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input, all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high-speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.

FEATUREs

• VCC = 1.65 V to 5.5 V

• All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V)

• All outputs VOUT (Max.) = 5.5 V (@VCC = 0 V or output off state)

• Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C)

• Typical VOH undershoot > 2.0 V (@VCC = 3.3 V, Ta = 25°C)

• High output current ±4 mA (@VCC = 1.65 V)

±8 mA (@VCC = 2.3 V)

±12 mA (@VCC = 2.7 V)

±24 mA (@VCC = 3.0 V to 5.5 V)