PMC-Sierra, Inc

PM5356 データシート - PMC-Sierra, Inc

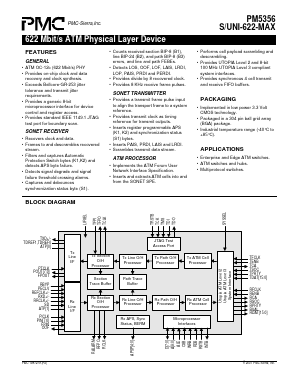

FEATURES

GENERAL

• ATM OC-12c (622 Mbit/s) PHY

• Provides on-chip clock and data recovery and clock synthesis.

• Exceeds Bellcore-GR-253 jitter tolerance and transmit jitter requirements.

• Provides a generic 8-bit microprocessor interface for device control and register access.

• Provides standard IEEE 1149.1 JTAG test port for boundary scan.

SONET RECEIVER

• Recovers clock and data.

• Frames to and descrambles recovered stream.

• Filters and captures Automatic Protection Switch bytes (K1,K2) and detects APS byte failure.

• Detects signal degrade and signal failure threshold crossing alarms.

• Captures and debounces synchronization status byte (S1).

• Counts received section BIP-8 (B1), line BIP-24 (B2), and path BIP-8 (B3) errors, and line and path FEBEs.

• Detects LOS, OOF, LOF, LAIS, LRDI, LOP, PAIS, PRDI and PERDI.

• Provides divide by 8 recovered clock.

• Provides 8 KHz receive frame pulses.

SONET TRANSMITTER

• Provides a transmit frame pulse input to align the transport frame to a system reference.

• Provides transmit clock as timing reference for transmit outputs.

• Inserts register programmable APS (K1, K2) and synchronization status (S1) bytes.

• Inserts PAIS, PRDI, LAIS and LRDI.

• Scrambles transmit data stream.

APPLICATIONS

• Enterprise and Edge ATM switches.

• ATM switches and hubs.

• Multiprotocol switches.