Micron Technology

MT4LC16M4H9DJ-6S データシート - Micron Technology

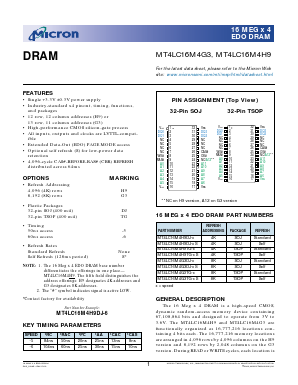

GENERAL DESCRIPTION

The 16 Meg x 4 DRAM is a high-speed CMOS, dynamic random-access memory device containing 67,108,864 bits and designed to operate from 3V to 3.6V. The MT4LC16M4H9 and MT4LC16M4G3 are functionally organized as 16,777,216 locations containing 4 bits each. The 16,777,216 memory locations are arranged in 4,096 rows by 4,096 columns on the H9 version and 8,192 rows by 2,048 columns on the G3 version.

FEATURES

• Single +3.3V ±0.3V power supply

• Industry-standard x4 pinout, timing, functions, and packages

• 12 row, 12 column addresses (H9) or 13 row, 11 column addresses (G3)

• High-performance CMOS silicon-gate process

• All inputs, outputs and clocks are LVTTL-compat ible

• Extended Data-Out (EDO) PAGE MODE access

• Optional self refresh (S) for low-power data retention

• 4,096-cycle CAS#-BEFORE-RAS# (CBR) REFRESH distributed across 64ms