STMicroelectronics

M54HC109K1 データシート - STMicroelectronics

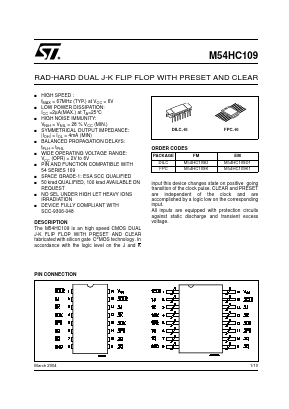

DESCRIPTION

The M54HC109 is an high speed CMOS DUAL J-K FLIP FLOP WITH PRESET AND CLEAR fabricated with silicon gate C2MOS technology. In accordance with the logic level on the J and K input this device changes state on positive going transition of the clock pulse. CLEAR and PRESET are independent of the clock and are accomplished by a logic low on the corresponding input.

All inputs are equipped with protection circuits against static discharge and transient excess voltage.

■ HIGH SPEED :

fMAX = 67MHz (TYP.) at VCC = 6V

■ LOW POWER DISSIPATION:

ICC =2µA(MAX.) at TA=25°C

■ HIGH NOISE IMMUNITY:

VNIH = VNIL = 28 % VCC (MIN.)

■ SYMMETRICAL OUTPUT IMPEDANCE:

|IOH| = IOL = 4mA (MIN)

■ BALANCED PROPAGATION DELAYS: tPLH ≅ tPHL

■ WIDE OPERATING VOLTAGE RANGE:

VCC (OPR) = 2V to 6V

■ PIN AND FUNCTION COMPATIBLE WITH 54 SERIES 109

■ SPACE GRADE-1: ESA SCC QUALIFIED

■ 50 krad QUALIFIED, 100 krad AVAILABLE ON REQUEST

■ NO SEL UNDER HIGH LET HEAVY IONS IRRADIATION

■ DEVICE FULLY COMPLIANT WITH SCC-9306-048