Sharp Electronics

LH6V4256D-10 データシート - Sharp Electronics

DESCRIPTION

The LH6V4256 is a 262,144 word × 4-bit dynamic RAM which allows fast page mode access. The LH6V4256 is fabricated on SHARP’s advanced CMOS double-level polysilicon gate technology. With its input multiplexed and packaged in the standard 20-pin DIP, 26-pin SOJ, or 28-pin TSOP (I) packages, it is easy to realize memory systems with low power dissipation and large memory capacity. The LH6V4256 operates on a single +3.3 V power supply and the built-in biasing voltage generator circuit.

FUNCTION

• 262,144 words × 4 bit

• Access time: 100 ns (MAX)

• Cycle time: 190 ns (MIN)

• Fast page mode cycle time: 60 ns (MIN)

• Power supply: +3.3 V ±0.3 V

• Power consumption (MAX):

Operating: 126 mW

Standby: 0.54 mW

• Built-in latch circuit for row-address, column-address, and input data

• OE = Don’t care in early write operation

• RAS only refresh, hidden refresh, and CAS before RAS refresh capability

• On-chip refresh counter

• 512 refresh cycle/8 ms

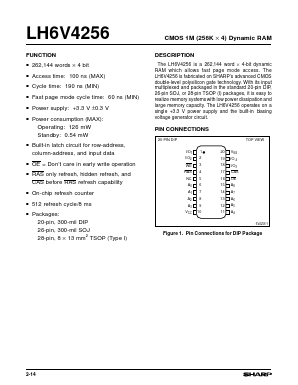

• Packages:

20-pin, 300-mil DIP

26-pin, 300-mil SOJ

28-pin, 8 × 13 mm2 TSOP (Type I)