Integrated Device Technology

IDT54FCT162601CT データシート - Integrated Device Technology

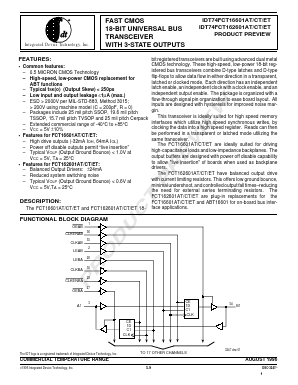

DESCRIPTION:

The FCT16601AT/CT/ET and FCT162601AT/CT/ET 18-bit registered transceivers are built using advanced dual metal CMOS technology. These high-speed, low-power 18-bit registered bus transceivers combine D-type latches and D-type flip-flops to allow data flow in either direction in a transparent, latched or clocked mode. Each direction has an independent latch enable, an independent clock with a clock enable, and an independent output enable. The package is organized with a flow-through signal pin organization to ease board layout. All inputs are designed with hysteresis for improved noise margin.

FEATURES:

• Common features: – 0.5 MICRON CMOS Technology

– High-speed, low-power CMOS replacement for ABT functions

– Typical tSK(o) (Output Skew) < 250ps

– Low input and output leakage ≤1µA (max.)

– ESD > 2000V per MIL-STD-883, Method 3015; > 200V using machine model (C = 200pF, R = 0)

– Packages include 25 mil pitch SSOP, 19.6 mil pitch TSSOP, 15.7 mil pitch TVSOP and 25 mil pitch Cerpack

– Extended commercial range of -40°C to +85°C

– VCC = 5V ±10%

• Features for FCT16601AT/CT/ET:

– High drive outputs (-32mA IOH, 64mA IOL)

– Power off disable outputs permit “live insertion”

– Typical VOLP (Output Ground Bounce) < 1.0V at VCC = 5V, TA = 25°C

• Features for FCT162601AT/CT/ET:

– Balanced Output Drivers: ±24mA

– Reduced system switching noise

– Typical VOLP (Output Ground Bounce) < 0.6V at VCC = 5V,TA = 25°C