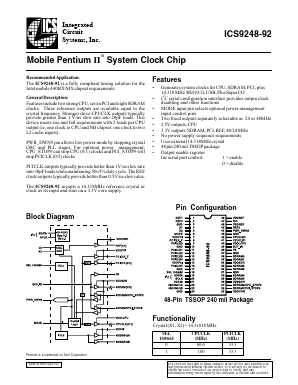

Integrated Circuit Systems

ICS9248-92 データシート - Integrated Circuit Systems

General Description:

Features include two strong CPU, seven PCI and eight SDRAM clocks. Three reference outputs are available equal to the crystal frequency. Stronger drive CPUCLK outputs typically provide greater than 1 V/ns slew rate into 20pF loads. This device meets rise and fall requirements with 2 loads per CPU output (ie, one clock to CPU and NB chipset, one clock to two L2 cache inputs).

FEATUREs

• Generates system clocks for CPU, SDRAM, PCI, plus 14.318 MHz REF(0:2), USB, Plus Super I/O

• I2C serial configuration interface provides output clock disabling and other functions

• MODE input pin selects optional power management input control pins

• Two fixed outputs separately selectable as 24 or 48MHz

• 2.5V outputs: CPU

• 3.3V outputs: SDRAM, PCI, REF, 48/24 MHz

• No power supply sequence requirements

• Uses external 14.318MHz crystal

• 48 pin 240 mil TSSOP package

• Output enable register

for serial port control: 1 = enable

0 = disable

Recommended Application:

The ICS9248-92 is a fully compliant timing solution for the Intel mobile 440BX/MX chipset requirements.