Integrated Circuit Systems

ICS8521I-03 データシート - Integrated Circuit Systems

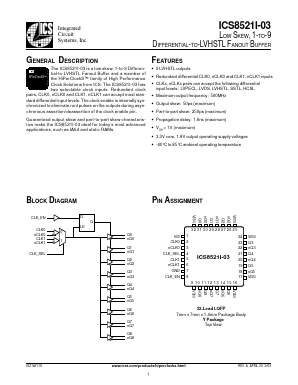

GENERAL DESCRIPTION

The ICS8521I-03 is a low skew, 1-to-9 Differential-to-LVHSTL Fanout Buffer and a member of the HiPerClockS™ family of High Performance Clock Solutions from ICS. The ICS8521I-03 has two selectable clock inputs. Redundant clock pairs, CLK0, nCLK0 and CLK1, nCLK1 can accept most standard differential input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin.

FEATURES

• 9 LVHSTL outputs

• Redundant differential CLK0, nCLK0 and CLK1, nCLK1 inputs

• CLKx, nCLKx pairs can accept the following differential input levels: LVPECL, LVDS, LVHSTL, SSTL, HCSL

• Maximum output frequency: 500MHz

• Output skew: 50ps (maximum)

• Part-to-part skew: 250ps (maximum)

• Propagation delay: 1.6ns (maximum)

• VOH = 1V (maximum)

• 3.3V core, 1.8V output operating supply voltages

• -40°C to 85°C ambient operating temperature