Intersil

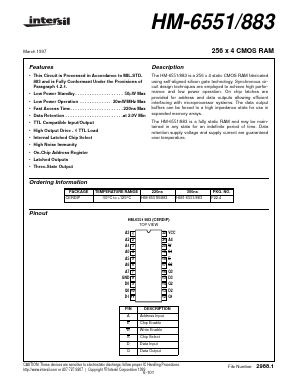

HM-6551/883(1997) データシート - Intersil

Description

The HM-6551/883 is a 256 x 4 static CMOS RAM fabricated using self-aligned silicon gate technology. Synchronous circuit design techniques are employed to achieve high performance and low power operation. On chip latches are provided for address and data outputs allowing efficient interfacing with microprocessor systems. The data output buffers can be forced to a high impedance state for use in expanded memory arrays.

FEATUREs

• This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

• Low Power Standby . . . . . . . . . . . . . . . . . . . . 50µW Max

• Low Power Operation . . . . . . . . . . . . . 20mW/MHz Max

• Fast Access Time. . . . . . . . . . . . . . . . . . . . . . 220ns Max

• Data Retention . . . . . . . . . . . . . . . . . . . . . . . .at 2.0V Min

• TTL Compatible Input/Output

• High Output Drive - 1 TTL Load

• Internal Latched Chip Select

• High Noise Immunity

• On-Chip Address Register

• Latched Outputs

• Three-State Output