AMI Semiconductor

FS61857-01 データシート - AMI Semiconductor

Description

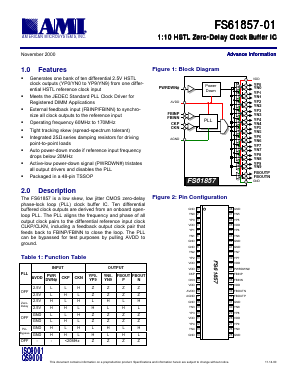

The FS61857 is a low skew, low jitter CMOS zero-delay phase-lock loop (PLL) clock buffer IC. Ten differential buffered clock outputs are derived from an onboard openloop PLL. The PLL aligns the frequency and phase of all output clock pairs to the differential reference input clock CLKP/CLKN, including a feedback output clock pair that feeds back to FBINP/FBINN to close the loop. The PLL can be bypassed for test purposes by pulling AVDD to ground.

FEATUREs

• Generates one bank of ten differential 2.5V HSTL clock outputs (YP0/YN0 to YP9/YN9) from one differential HSTL reference clock input

• Meets the JEDEC Standard PLL Clock Driver for Registered DIMM Applications

• External feedback input (FBINP/FBINN) to synchronize all clock outputs to the reference input

• Operating frequency 60MHz to 170MHz

• Tight tracking skew (spread-spectrum tolerant)

• Integrated 25Ω series damping resistors for driving point-to-point loads

• Auto power-down mode if reference input frequency drops below 20MHz

• Active-low power-down signal (PWRDWN#) tristates all output drivers and disables the PLL

• Packaged in a 48-pin TSSOP