Advanced Micro Devices

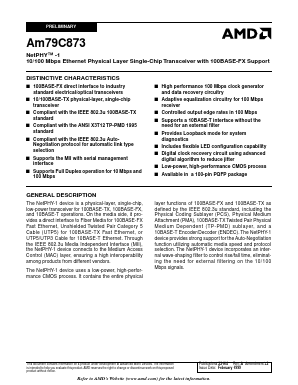

AM79C873KC データシート - Advanced Micro Devices

GENERAL DESCRIPTION

The NetPHY-1 device is a physical-layer, single-chip, low-power transceiver for 100BASE-TX, 100BASE-FX, and 10BASE-T operations. On the media side, it provides a direct interface to Fiber Media for 100BASE-FX Fast Ethernet, Unshielded Twisted Pair Category 5 Cable (UTP5) for 100BASE-TX Fast Ethernet, or UTP5/UTP3 Cable for 10BASE-T Ethernet. Through the IEEE 802.3u Media Independent Interface (MII), the NetPHY-1 device connects to the Medium Access Control (MAC) layer, ensuring a high interoperability among products from different vendors.

The NetPHY-1 device uses a low-power, high-performance CMOS process. It contains the entire physical layer functions of 100BASE-FX and 100BASE-TX as defined by the IEEE 802.3u standard, including the Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), 100BASE-TX Twisted Pair Physical Medium Dependent (TP-PMD) sublayer, and a 10BASE-T Encoder/Decoder (ENDEC). The NetPHY-1 device provides strong support for the Auto-Negotiation function utilizing automatic media speed and protocol selection. The NetPHY-1 device incorporates an internal wave-shaping filter to control rise/fall time, eliminating the need for external filtering on the 10/100 Mbps signals.

DISTINCTIVE CHARACTERISTICS

■ 100BASE-FX direct interface to industry

standard electrical/optical transceivers

■ 10/100BASE-TX physical-layer, single-chip transceiver

■ Compliant with the IEEE 802.3u 100BASE-TX standard

■ Compliant with the ANSI X3T12 TP-PMD 1995 standard

■ Compliant with the IEEE 802.3u Auto

Negotiation protocol for automatic link type selection

■ Supports the MII with serial management interface

■ Supports Full Duplex operation for 10 Mbps and 100 Mbps

■ High performance 100 Mbps clock generator

and data recovery circuitry

■ Adaptive equalization circuitry for 100 Mbps receiver

■ Controlled output edge rates in 100 Mbps

■ Supports a 10BASE-T interface without the

need for an external filter

■ Provides Loopback mode for system diagnostics

■ Includes flexible LED configuration capability

■ Digital clock recovery circuit using advanced

digital algorithm to reduce jitter

■ Low-power, high-performance CMOS process

■ Available in a 100-pin PQFP package