NXP Semiconductors.

74HC590 データシート - NXP Semiconductors.

General description

The 74HC590 is a high-speed Si-gate CMOS device and is pin compatible with Low power Schottky TTL (LSTTL). It is specified in compliance with JEDEC standard no. 7A.

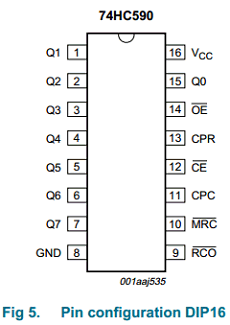

The 74HC590 is an 8-bit binary counter with a storage register and 3-state outputs. The storage register has parallel (Q0 to Q7) outputs. The binary counter features a master reset counter (MRC) and count enable (CE) inputs. The counter and storage register have separate positive edge triggered clock (CPC and CPR) inputs. If both clocks are connected together, the counter state always is one count ahead of the register. Internal circuitry prevents clocking from the clock enable. A ripple carry output (RCO) is provided for cascading. Cascading is accomplished by connecting RCO of the first stage to CE of the second stage. Cascading for larger count chains can be accomplished by connecting RCO of each stage to the counter clock (CPC) input of the following stage. If both clocks are connected together, the counter state always is one count ahead of the register.

FEATUREs

■ Counter and register have independent clock inputs

■ Counter has master reset

■ Complies with JEDEC standard no. 7A

■ Multiple package options

■ ESD protection:

◆ HBM JESD22-A114E exceeds 2000 V

◆ MM JESD22-A115-A exceeds 200 V

◆ CDM JESD22-C101C exceeds 2000 V

■ Specified from −40 °C to +85 °C and from −40 °C to +125 °C