AD7298-1BCPZ-RL データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD7298-1BCPZ-RL Datasheet PDF : 24 Pages

| |||

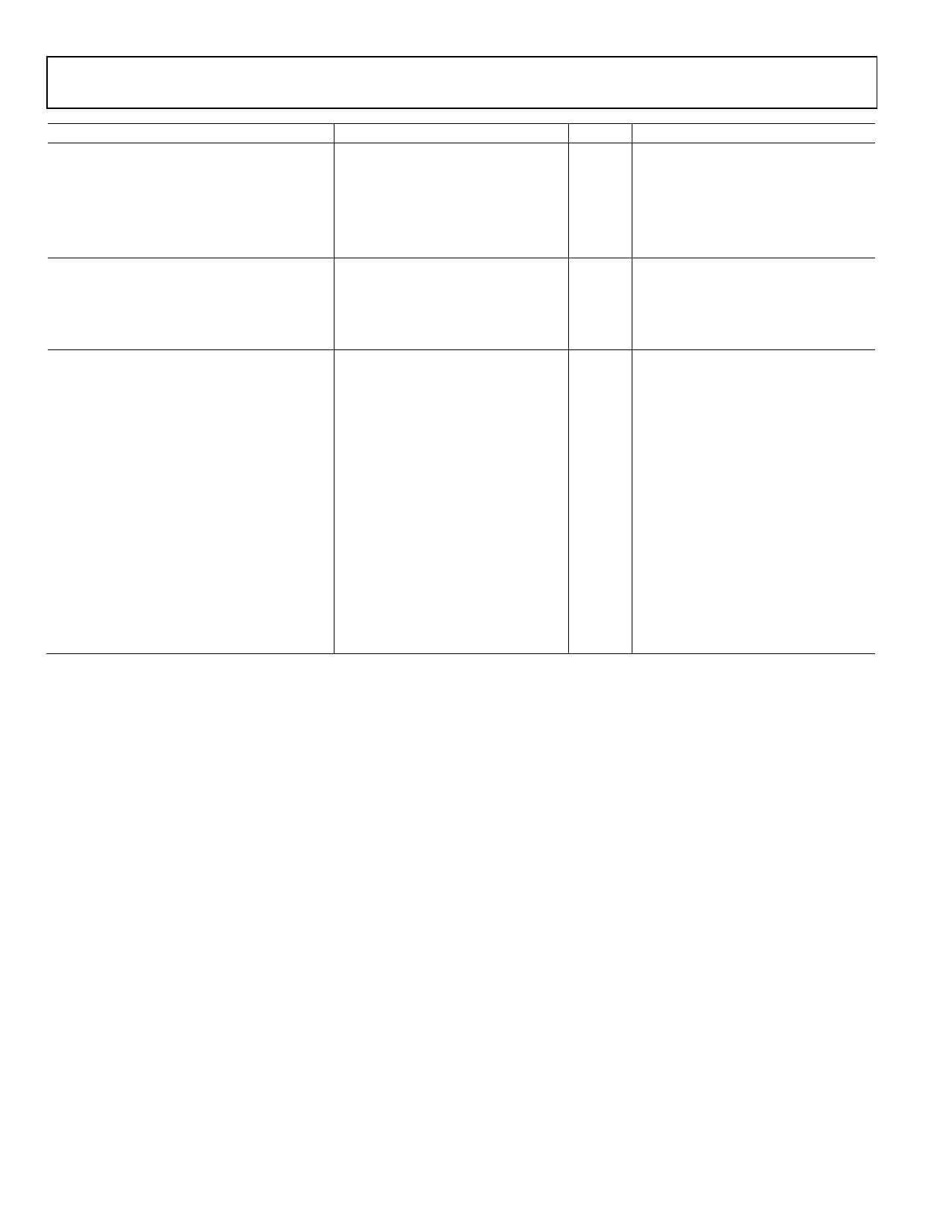

AD7298-1

Parameter

LOGIC OUTPUTS

Output High Voltage, VOH

Output Low Voltage, VOL

Floating State Leakage Current

Floating State Output Capacitance3

CONVERSION RATE

Conversion Time

Track-and-Hold Acquisition Time2, 3

Throughput Rate

POWER REQUIREMENTS

VDD

VDRIVE

ITOTAL5

Normal Mode (Operational)

Normal Mode (Static)

Partial Power-Down Mode

Full Power-Down Mode

Power Dissipation6

Normal Mode (Operational)

Normal Mode (Static)

Partial Power-Down Mode

Full Power-Down Mode

Min

Typ

Max

Unit

VDRIVE − 0.3

V

VDRIVE − 0.2

V

0.4

V

±0.01 ±1

μA

8

pF

1

t2 + (16 × tSCLK) μs

100

ns

1

MSPS

2.8

3

3.6

V

1.65

3

3.6

V

5.8

6.4

mA

4.1

4.6

mA

2.7

3.3

mA

1

1.6

μA

10

μA

17.4 19.2

mW

23

mW

14.8 16.6

mW

9.8

11.9

mW

3.6

5.8

μW

36

μW

Test Conditions/Comments

VDRIVE < 1.8

VDRIVE ≥ 1.8

For VIN0 to VIN7 with one cycle latency

Full-scale step input

fSCLK = 20 MHz; for analog voltage

conversions, one cycle latency

Digital inputs = 0 V or VDRIVE

VDD = 3.6 V, VDRIVE = 3.6 V

TA = −40°C to +25°C

TA = −40°C to +125°C

VDD = 3 V, VDRIVE = 3 V

TA = −40°C to +25°C

TA = −40°C to +125°C

1 All specifications expressed in decibels are referred to full-scale input FSR and tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

2 See the Terminology section.

3 Sample tested during initial release to ensure compliance.

4 Refers to the VREF pin specified for 25°C.

5 ITOTAL is the total current flowing in VDD and VDRIVE.

6 Power dissipation is specified with VDD = VDRIVE = 3.6 V, unless otherwise noted.

Rev. A | Page 4 of 24