OX16PCI952 データシートの表示(PDF) - Oxford Semiconductor

部品番号

コンポーネント説明

メーカー

OX16PCI952

Oxford Semiconductor

OX16PCI952 Datasheet PDF : 77 Pages

| |||

OXFORD SEMICONDUCTOR LTD.

OX16PCI952

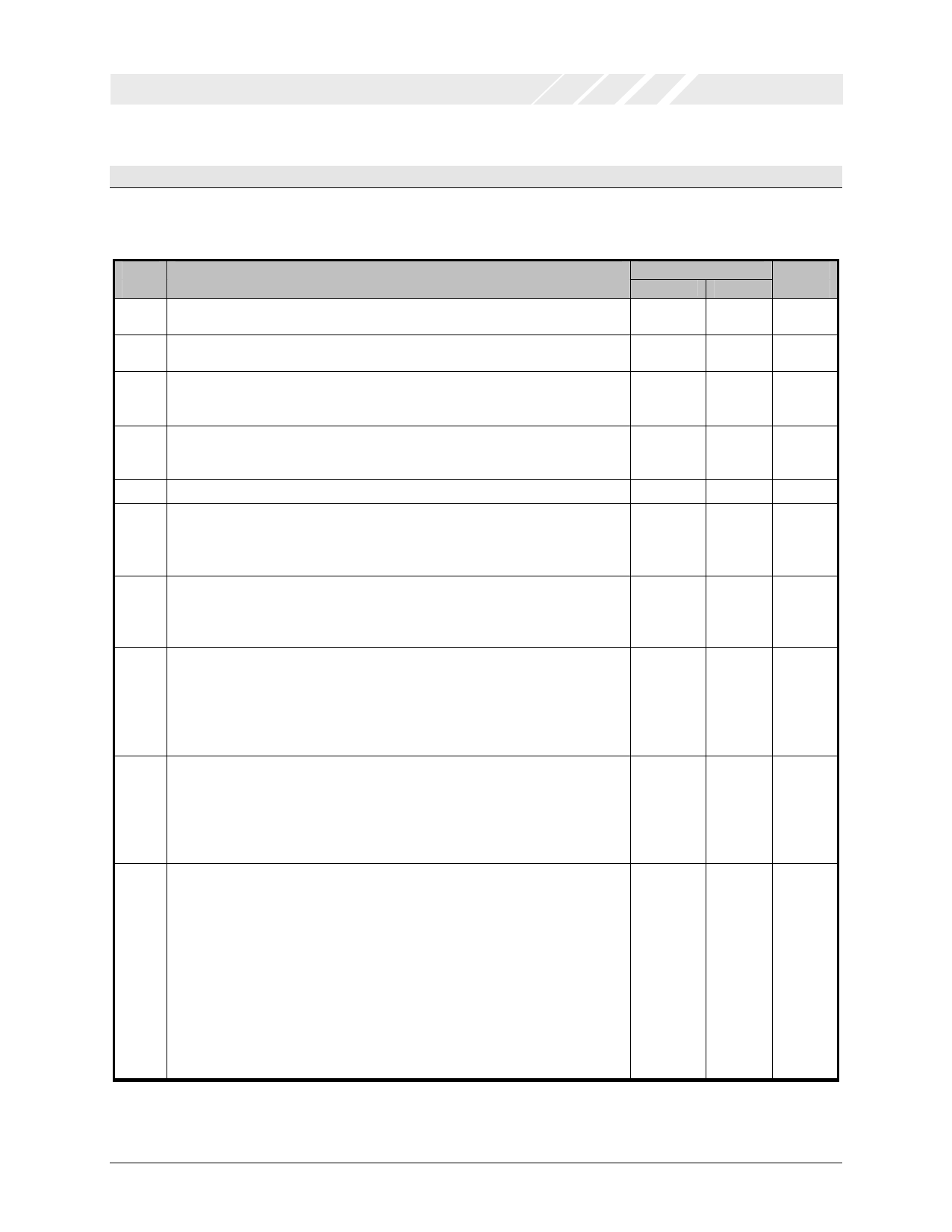

6.4.5 Global Interrupt Status and Control Register ‘GIS’ (Offset 0x10)

This register controls the assertion of interrupts and power management events, as well as returning the internal status of all

interrupt sources and power management events.

Bits Description

Read/Write

EEPROM PCI

0

UART 0 internal interrupt status.

-

R

This bit reflects the state of UART 0’s internal interrupt line1.

1

UART 1 internal interrupt status.

-

R

This bit reflects the state of UART 1’s internal interrupt line1.

2

MIO0 Internal State.

-

R

This bit reflects the state of the internal MIO[0] signal. The internal MIO[0]

signal reflects the non-inverted or inverted state of MIO0 pin. 2

3

MIO1 Internal State

-

R

This bit reflects the state of the internal MIO[1] signal. The internal MIO[1]

reflects the non-inverted or inverted state of MIO1 pin. 2

15:4 Reserved.

-

R

Reset

0x0h

0x0h

X

X

000h

16 UART 0 Interrupt Mask.

W

RW

1

When set (=1) this bit enables UART 0 to assert a PCI interrupt on function 0’s

interrupt pin (INTA# by default). When cleared (=0), UART 0 is prevented from

asserting a PCI interrupt.3

17 UART 1 Interrupt Mask.

W

RW

1

When set (=1) this bit enables UART 1 to assert a PCI interrupt on function 0’s

interrupt pin (INTA# by default). When cleared (=0), UART 1 is prevented from

asserting a PCI interrupt.3

18 MIO 0 Interrupt Mask.

W

RW

0

When set (=1) this bit enables the MIO 0 pin to assert a PCI interrupt, on the

selected function’s interrupt pin. When cleared (=0) this prevents MIO 0 from

asserting a PCI interrupt.

The function that is affected is controlled by GIS, bit 26.

The MIO 0 pin is active high, unless inversion has been set in the MIC register

19 MIO 1 Interrupt Mask.

W

RW

0

When set (=1) this bit enables the MIO 1 pin to assert a PCI interrupt, on the

selected function’s interrupt pin. When cleared (=0) this prevents MIO 1 from

asserting a PCI interrupt.

The function that is affected is controlled by GIS, bit 27.

The MIO 1 pin is active high, unless inversion has been set in the MIC register

20 MIO 0 Power-down Mask.

W

RW

0

When set (=1) this bit enables the MIO 0 pin to issue a powerdown event by

setting the selected function’s power-down sticky bit (GIS, bits 22 or 23).

The function whose powerdown sticky bit is affected is controlled by GIS, bit

26.

Note that if the MIO 0 pin is routed to Function 0, then the pin uses the UART

power-down filtering algorithm. Both the UARTs and the MIO 0 pin must

indicate a power-down for the filter period before any powerdown requests are

issued, for function 0. However, when the MIO 0 pin is routed to Function 1,

then a powerdown state on the pin MIO 0 will immediately issue a powerdown

request, for function 1, without any filters.

DS-0028 Jul 05

External-Free Release

Page 23