MT46V16M16BG-75ZL データシートの表示(PDF) - Micron Technology

部品番号

コンポーネント説明

メーカー

MT46V16M16BG-75ZL Datasheet PDF : 80 Pages

| |||

256Mb: x4, x8, x16

DDR SDRAM

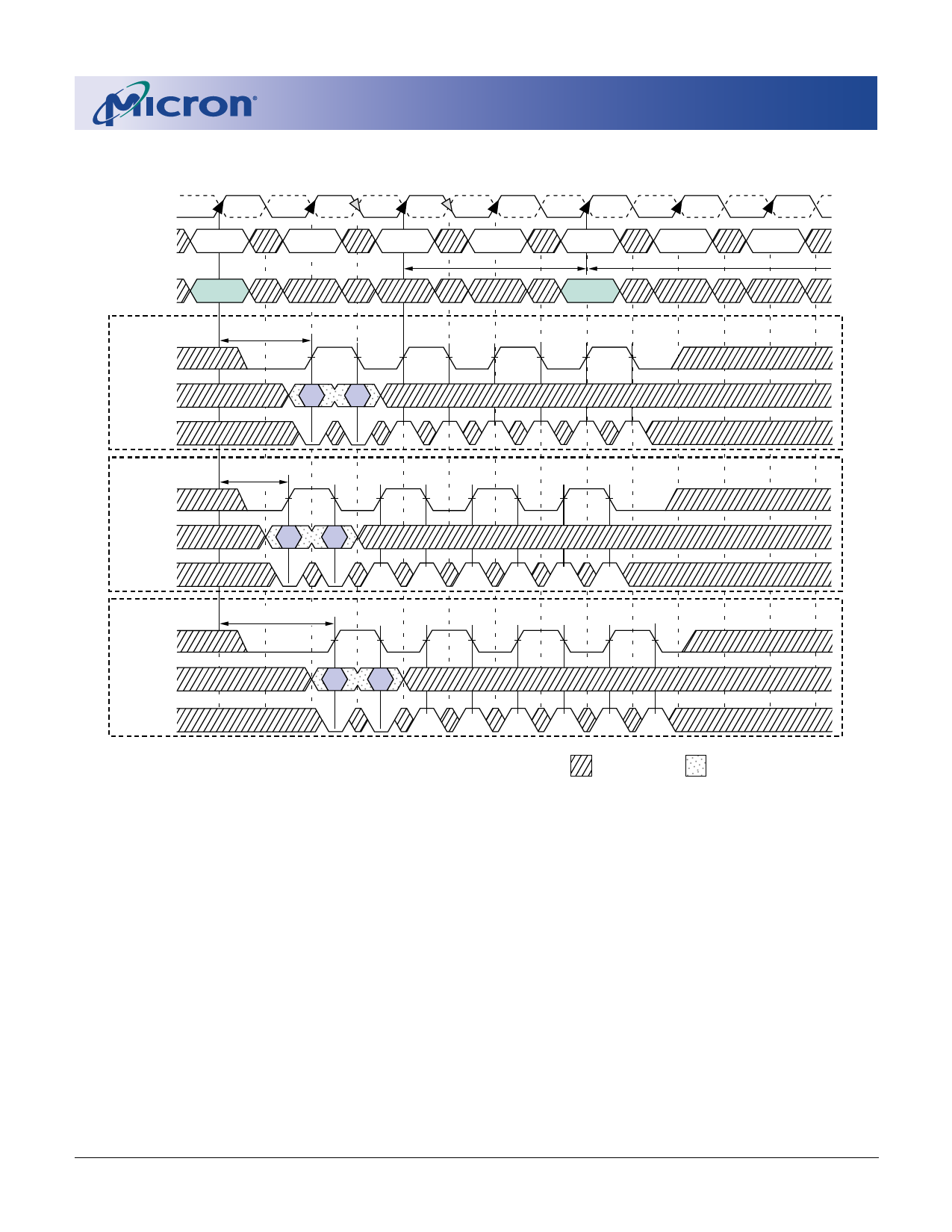

CK#

CK

COMMAND

ADDRESS

Figure 29: WRITE to PRECHARGE – Interrupting

T0

T1 T1n T2 T2n T3 T3n T4 T4n T5

WRITE

NOP

Bank a,

Col b

NOP

NOP

PRE8

NOP

tWR

Bank,

(a or all)

tDQSS (NOM)

DQS

tDQSS

DQ

DI

b

DM

T6

NOP

tRP

tDQSS (MIN)

DQS

DQ

DM

tDQSS

DI

b

tDQSS (MAX)

DQS

tDQSS

DQ

DI

b

DM

DON’T CARE

NOTE:

1. DI b = data-in for column b.

2. Subsequent element of data-in is applied in the programmed order following DI b.

3. An interrupted burst of 8 is shown; two data elements are written.

4. tWR is referenced from the first positive CK edge after the last data-in pair.

5. A10 is LOW with the WRITE command (auto precharge is disabled).

6. DQS is required at T4 and T4n (nominal case) to register DM.

7. If the burst of 4 was used, DQS and DM would not be required at T3, T3n, T4, and T4n.

8. PRE = PRECHARGE command.

TRANSITIONING DATA

09005aef8076894f

256MBDDRx4x8x16_2.fm - Rev. F 6/03 EN

38

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2003 Micron Technology, Inc.