74AHC08 データシートの表示(PDF) - NXP Semiconductors.

部品番号

コンポーネント説明

メーカー

74AHC08 Datasheet PDF : 14 Pages

| |||

Nexperia

74AHC08; 74AHCT08

Quad 2-input AND gate

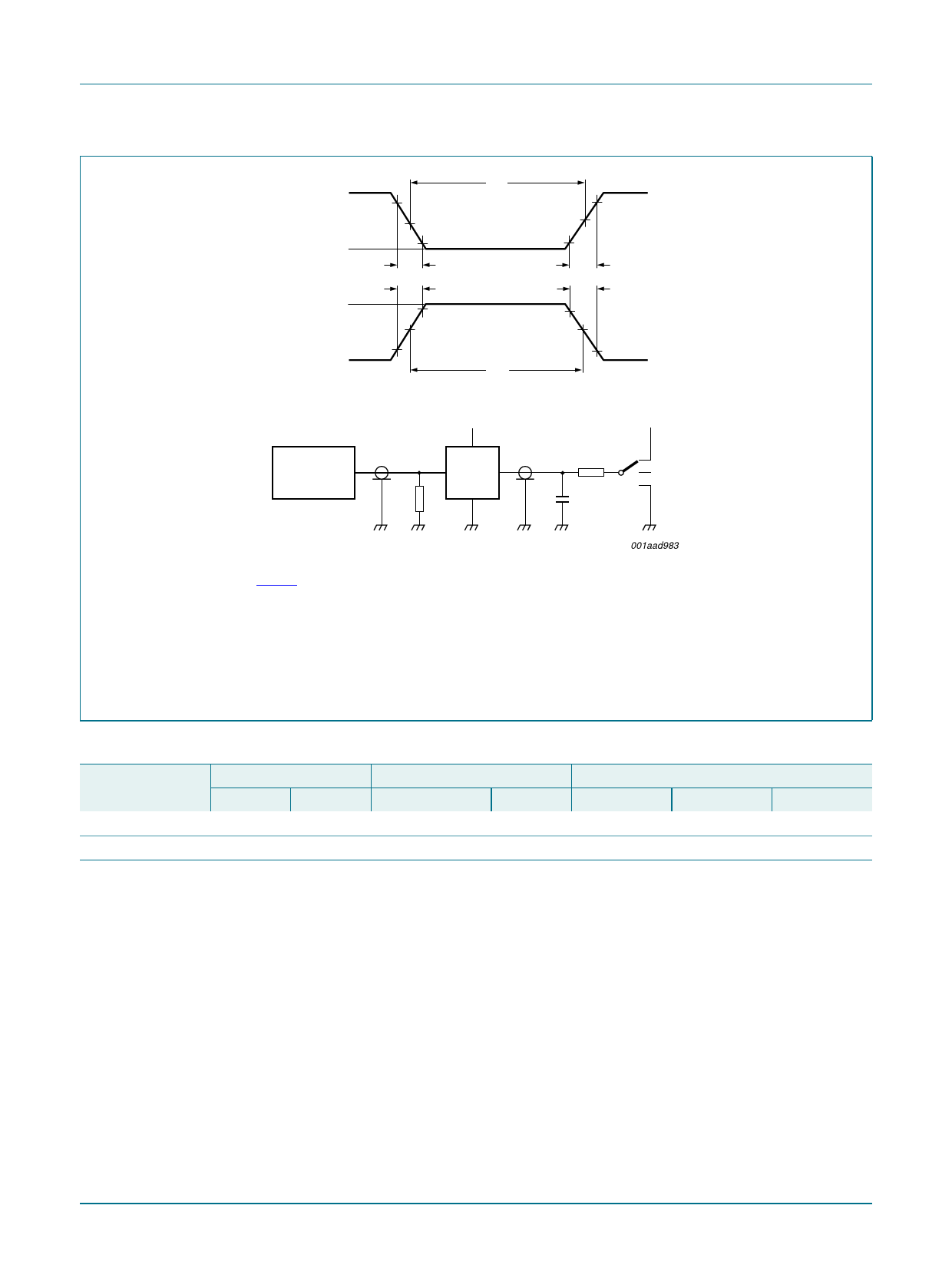

VI 90 %

tW

negative

pulse

VM

10 %

0V

tf

VI

positive

pulse

tr

90 %

VM

10 %

0V

tW

VM

tr

tf

VM

PULSE

VI

GENERATOR

VCC

VO

DUT

RT

VCC

RL S1

CL

open

001aad983

Test data is given in Table 9.

Definitions test circuit:

RT = Termination resistance should be equal to output impedance Zo of the pulse generator.

CL = Load capacitance including jig and probe capacitance.

RL = Load resistance.

S1 = Test selection switch.

Fig 7. Load circuit for switching times

Table 9. Test data

Type

Input

VI

74AHC08

VCC

74AHCT08

3.0 V

tr, tf

≤ 3.0 ns

≤ 3.0 ns

Load

CL

15 pF, 50 pF

15 pF, 50 pF

RL

1 kΩ

1 kΩ

S1 position

tPHL, tPLH

open

open

tPZH, tPHZ

GND

GND

tPZL, tPLZ

VCC

VCC

74AHC_AHCT08_3

Product data sheet

Rev. 03 — 14 November 2007

© Nexperia B.V. 2017. All rights reserved

8 of 14