74LVC16373 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

メーカー

74LVC16373

Philips Electronics

74LVC16373 Datasheet PDF : 17 Pages

| |||

Philips Semiconductors

16-bit D-type transparent latch with 5 V

tolerant inputs/outputs; 3-state

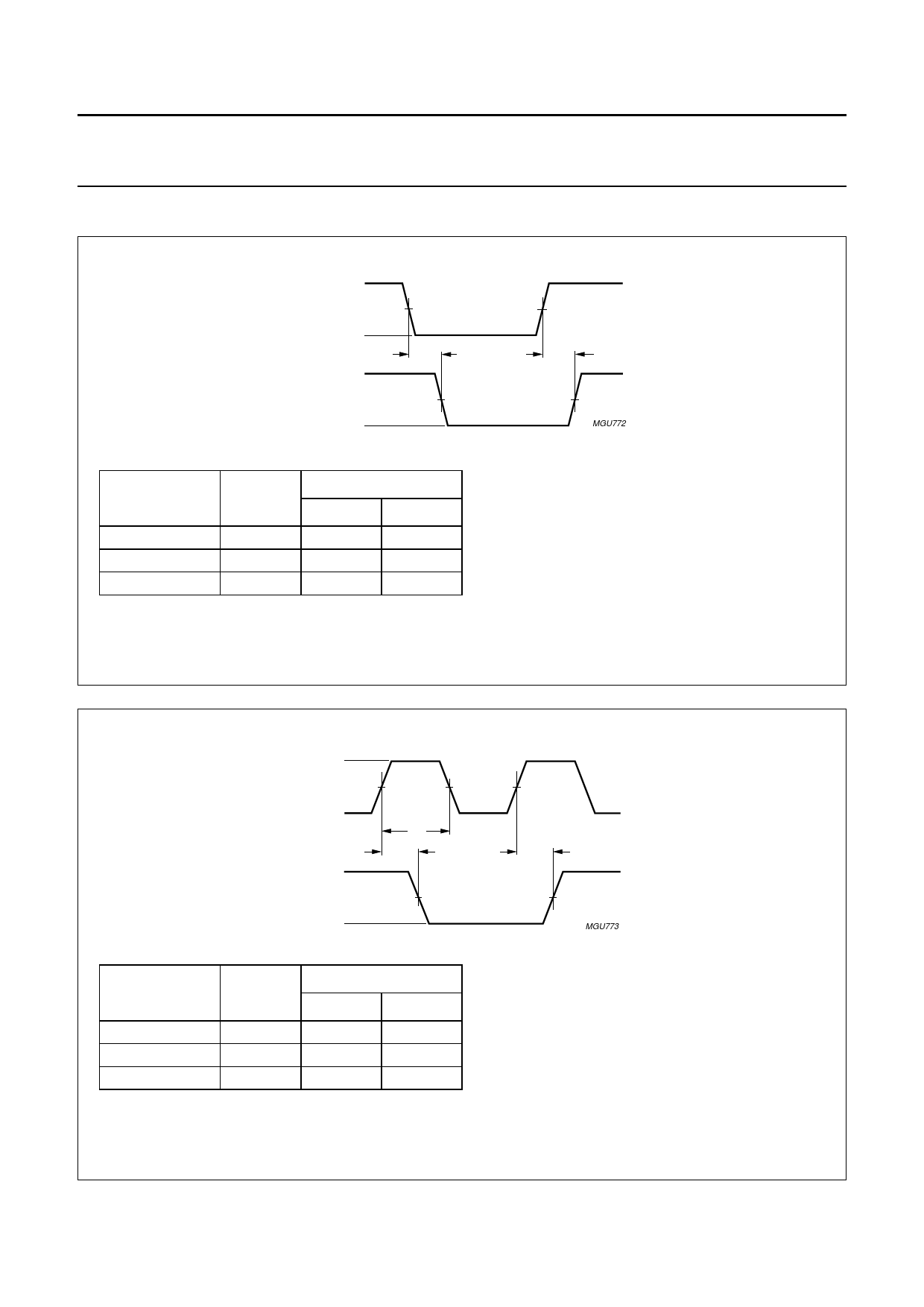

AC WAVEFORMS

Product specification

74LVC16373A;

74LVCH16373A

handbook, halfpagVeI

Dn input

GND

VOH

Qn output

VOL

VM

t PHL

VM

VM

t PLH

MGU772

VCC

1.2 V

2.7 V

3.0 to 3.6 V

VM

0.5 × VCC

1.5 V

1.5 V

INPUT

VI

VCC

2.7 V

2.7 V

tr = tf

≤ 2.5 ns

≤ 2.5 ns

≤ 2.5 ns

VOL and VOH are the typical output voltage drop that occur with the output load.

Fig.6 Input (Dn) to output (Qn) propagation delays.

handbook, hValfIpage

LE input

GND

VOH

Qn output

VOL

VM

VM

tW

t PHL

VM

VM

t PLH

VM

MGU773

VCC

1.2 V

2.7 V

3.0 to 3.6 V

VM

0.5 × VCC

1.5 V

1.5 V

INPUT

VI

VCC

2.7 V

2.7 V

tr = tf

≤ 2.5 ns

≤ 2.5 ns

≤ 2.5 ns

VOL and VOH are the typical output voltage drop that occur with the output load.

Fig.7 Latch enable input (LE) pulse width, and the latch enable input to output (Qn) propagation delays.

2003 Dec 08

11