M35060-XXXSP データシートの表示(PDF) - Mitsumi

部品番号

コンポーネント説明

メーカー

M35060-XXXSP Datasheet PDF : 42 Pages

| |||

MITSUBISHI MICROCOMPUTERS

M35060-XXXSP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

MEMORY CONSTRUCTION

Address 00016 to 2A716 are assigned to the display RAM, 2A816 to

2B016 are assigned to the display control registers and 30016 to

6EC16 are assigned to SYRAM.

The internal circuit is reset and all display control registers (address

2A816 to 2B016) are set to “0”. The memory constitution of display

RAM and register is shown in Figure 1 and the memory constitution

of SYRAM is shown in Figure 2.

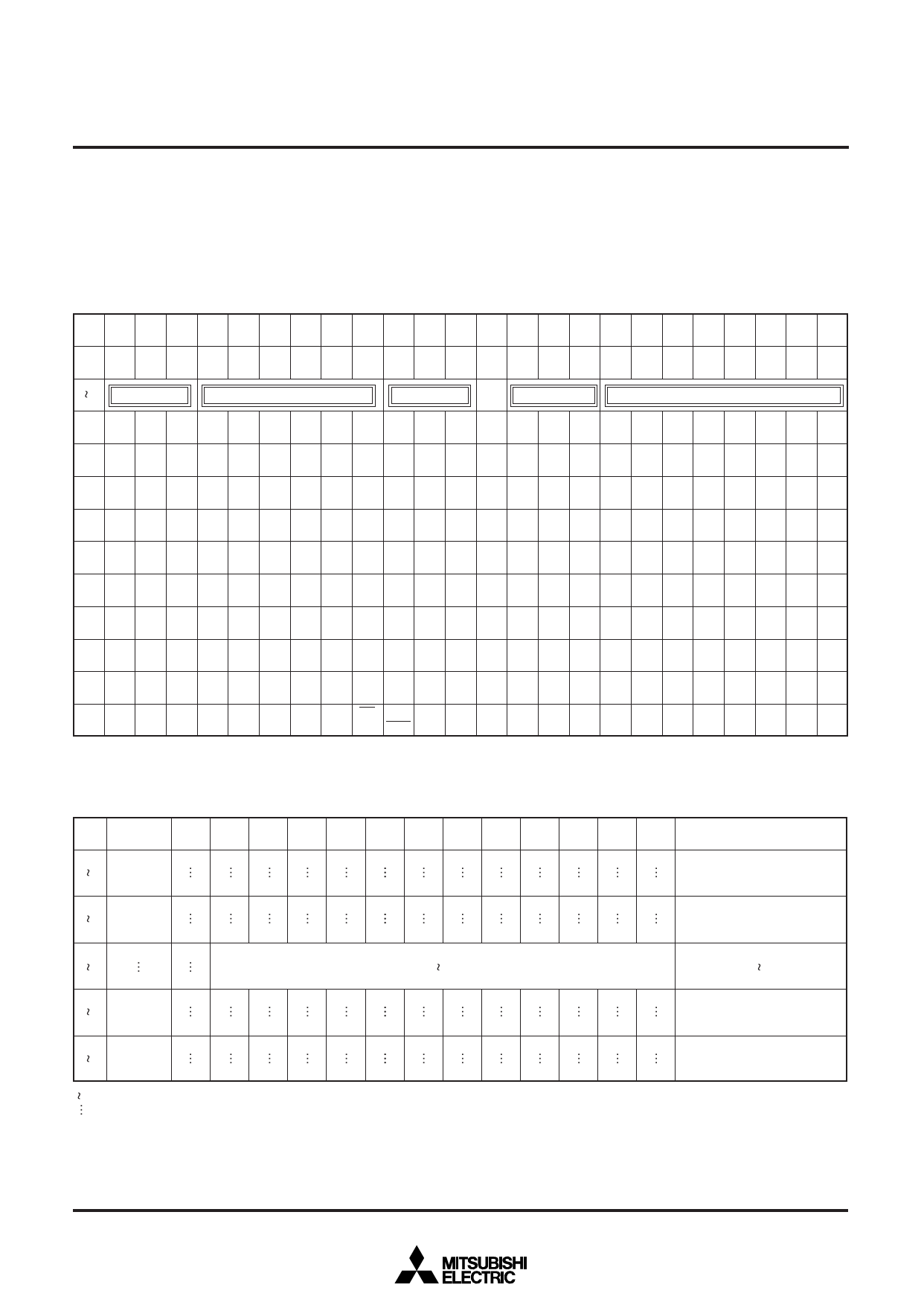

Table 1 The memory constitution of display RAM and register

add-

ress

DA17

DA16

DA15 DA14

DA13

DA12

DA11

DA10

DAF

DAE

DAD

DAC

DAB

DAA

DA9

DA8

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

00016 SB SG SR SYC5 SYC4 SYC3 SYC2 SYC1 SYC0 BB BG BR BLINK CB CG CR C7 C6 C5 C4 C3 C2 C1 C0

SY color setting

SYRAM setting

Raster color setting BLINK Character color setting

Character setting

2A716 SB SG SR SYC5 SYC4 SYC3 SYC2 SYC1 SYC0 BB BG BR BLINK CB CG CR C7 C6 C5 C4 C3 C2 C1 C0

2A816

–

TEST

3

TEST

2

TEST

1

TEST

0

TEST

11

TEST

10

HP8

HP7

HP6

HP5

HP4

HP3

HP2

HP1

HP0

VP7

VP6

VP5

VP4

VP3

VP2

VP1

VP0

2A916 –

–

–

BLINK BLINK BLINK BLINK HSZ

3 2 1 0 16

HSZ

15

HSZ

14

HSZ

13

HSZ

12

HSZ

11

HSZ

10

HSZ

9

HSZ

8

HSZ

7

HSZ

6

HSZ

5

HSZ

4

HSZ

3

HSZ

2

HSZ

1

HSZ

0

2AA16 –

–

–

TEST

12

EQP

TEST

20

HIDE

VSZ

16

VSZ

15

VSZ

14

VSZ

13

VSZ

12

VSZ VSZ VSZ VSZ VSZ VSZ VSZ VSZ VSZ VSZ VSZ VSZ

11 10 9 8 7 6 5 4 3 2 1 0

2AB16 –

–

TEST TEST PHASE PHASE PHASE DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0 DSP0

26 25 2 1 0 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

2AC16 –

–

–

TEST LINE LINE LINE DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1 DSP1

21 B G R 16 15 14 13 12 11 10 09 08 07 06 05 04 03 02 01 00

2AD16

–

TEST TEST SERS SERS SERS SERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS ERS

23 22 3 2 1 0 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

2AE16 –

–

–

–

–

SEND SEND SEND SEND SEND SST

432104

SST

3

SST

2

SST

1

SST SLIN SLIN SLIN SLIN SLIN SBIT SBIT SBIT SBIT

0432103210

2AF16

PC7

PC6

PC5

PC4

PC3

PC2

PC1

PC0

ALL24

SRAND

2

SRAND

1

SRAND

0

PTD

5

PTD

4

PTD

3

PTD

2

PTD

1

PTD

0

PTC

5

PTC

4

PTC

3

PTC

2

PTC

1

PTC

0

2B016

–

TEST

19

TEST

18

TEST

17

TEST LEVEL LEVEL LEVEL

24 2 1 0

INT

NON

PAL

NTSC

MPAL

PALH

TEST

16

TEST

15

SEPV1

SEPV0

BLK

–

DSP DSP

ONV ON

–

SEL

COR

–

EX

TESTn (n = number) is MITSUBISHI test memory. Set 0 to all bits.

Table 2 The memory constitution of SYRAM

add-

ress

DA17 ~ DAD

DAC

DAB

DAA

DA9

DA8

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

30016

SYEX S00B S00A S009 S008 S007 S006 S005 S004 S003 S002 S001 S000

0

30C16

SYEX S00B S00A S009 S008 S007 S006 S005 S004 S003 S002 S001 S000

31016

SYEX S01B S01A S019 S018 S017 S016 S015 S014 S013 S012 S011 S010

0

31C16

SYEX S01B S01A S019 S018 S017 S016 S015 S014 S013 S012 S011 S010

SYRAM code

0016

0116

6D016

SYEX S3DB S3DA S3D9 S3D8 S3D7 S3D6 S3D5 S3D4 S3D3 S3D2 S3D1 S3D0

0

6DC16

SYEX S3DB S3DA S3D9 S3D8 S3D7 S3D6 S3D5 S3D4 S3D3 S3D2 S3D1 S3D0

6E016

SYEX S3EB S3EA S3E9 S3E8 S3E7 S3E6 S3E5 S3E4 S3E3 S3E2 S3E1 S3E0

0

6EC16

SYEX S3EB S3EA S3E9 S3E8 S3E7 S3E6 S3E5 S3E4 S3E3 S3E2 S3E1 S3E0

: Name or value changes by definite ratio.

: The same name or value continues.

3D16

3E16

4