CY14B101Q1-SFXI データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY14B101Q1-SFXI Datasheet PDF : 27 Pages

| |||

CY14B101Q1

CY14B101Q2

CY14B101Q3

Hardware STORE Cycle

Over the Operating Range

Parameter

Description

tPHSB

Hardware STORE pulse width

CY14B101Q3

Unit

Min

Max

15

–

ns

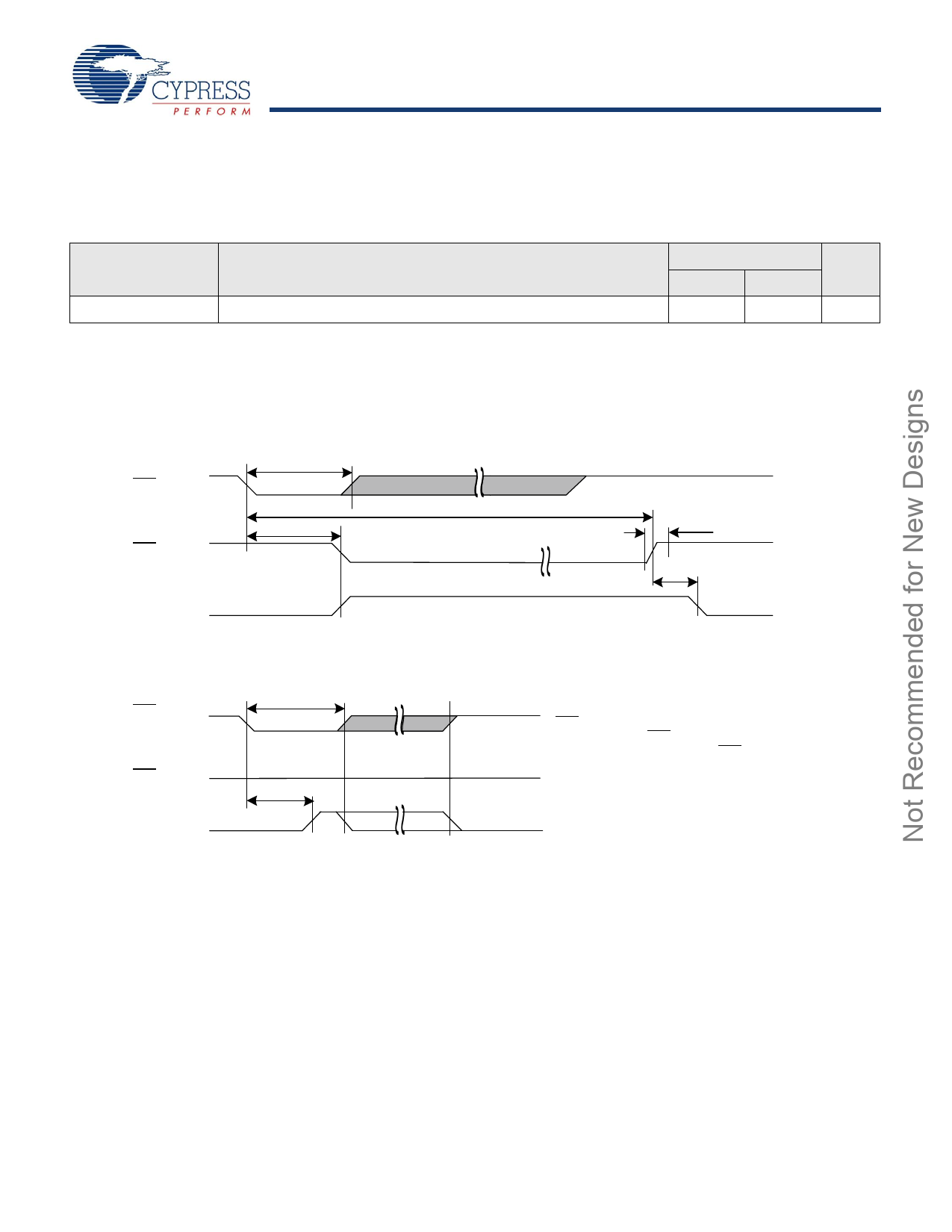

Switching Waveforms

Figure 28. Hardware STORE Cycle [20]

Write Latch set

HSB (IN)

tPHSB

HSB (OUT)

tDELAY

tSTORE

RWI

tHHHD

tLZHSB

Write Latch not set

HSB (IN)

tPHSB

HSB (OUT)

RWI

tDELAY

HSB pin is driven HIGH to VCC only by Internal

100 K: resistor, HSB driver is disabled

SRAM is disabled as long as HSB (IN) is driven LOW.

Note

20. If an SRAM write has not taken place since the last nonvolatile cycle, no AutoStore or Hardware STORE takes place.

Document Number: 001-50091 Rev. *L

Page 20 of 27