AS4LC1M16S1-8TC データシートの表示(PDF) - Alliance Semiconductor

部品番号

コンポーネント説明

メーカー

AS4LC1M16S1-8TC Datasheet PDF : 28 Pages

| |||

AS4LC2M8S1

AS4LC1M16S1

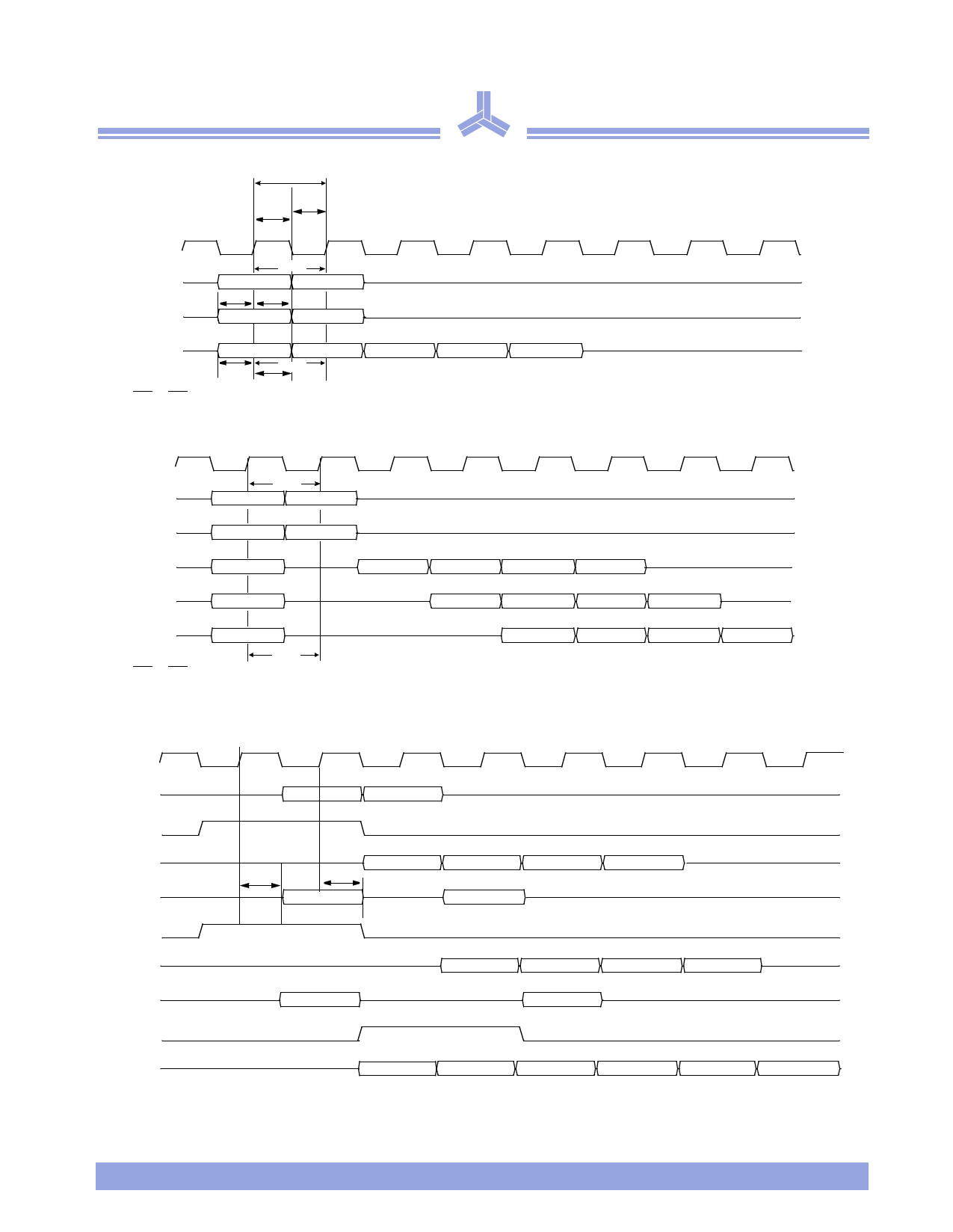

write interrupted by write (BL = 4)

tCK

CLK

CMD

tCH

tCL

tCCD

Write data

Write data

ADD

A0

B0

DQ

DA0

DB0

DB1

DB2

tDS

tCDL

tDH

tCCD = CAS to CAS delay (= 1 CLK).

tCDL = last address in to new column addres delay (= 1 CLK).

CLK

CMD

tCCD

Write data

Read data

ADD

A

B

DQ (CL1)

DA0

QB0

QB1

DQ (CL2)

DA0

QB0

DQ (CL3)

DA0

tCDL

tCCD = CAS to CAS delay (= 1 CLK).

tCDL = last address in to new column addres delay (= 1 CLK).

Interrupting RD/WR can be for either the same or different banks.

CLK

CMD1

DQM1

Read data

Write data

DQ1

CMD2

DQM2

tLZ

D0

tHZ

Read data

D1

Write data

DQ2

CMD3

DQM3

D0

Read data

DQ3

Q0

Q1

To prevent bus contention, maintain a gap between data in and data out.

DB3

write interrupted by read (BL = 4)

QB2

QB3

QB1

QB2

QB3

QB0

QB1

QB2

QB3

read interrupted by write (CL = 1, BL = 4)

D2

D3

D1

D2

D3

Write data

D0

D1

D2

D3

7/5/00

ALLIANCE SEMICONDUCTOR

19