ADSP-21266 データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

ADSP-21266 Datasheet PDF : 48 Pages

| |||

ADSP-21261/ADSP-21262/ADSP-21266

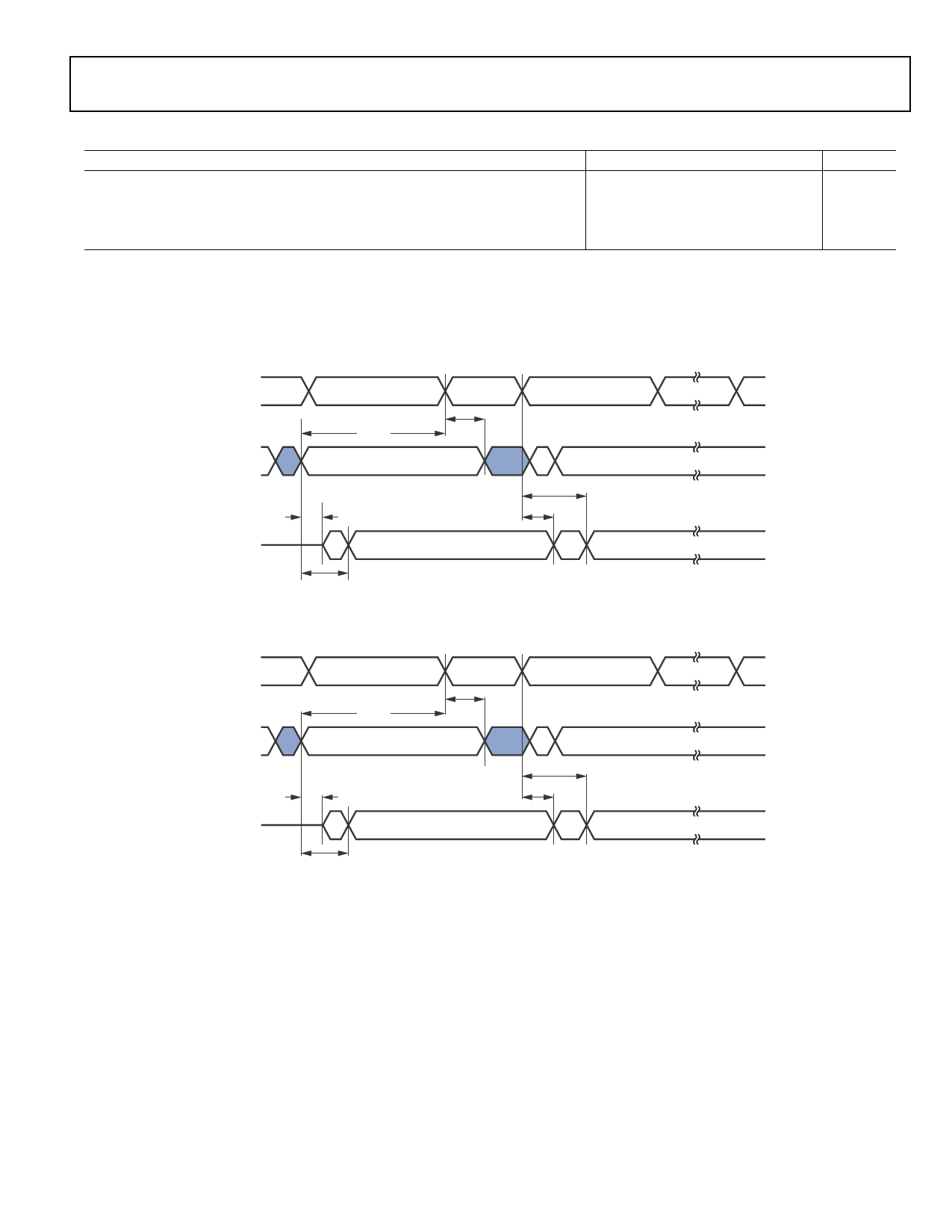

Table 32. Serial Ports—External Late Frame Sync

Parameter

Min

Switching Characteristics

tDDTLFSE

Data Delay from Late External Transmit FS or External Receive FS with

MCE = 1, MFD = 01

tDDTENFS

Data Enable for MCE = 1, MFD = 01

0.5

1 The tDDTLFSE and tDDTENFS parameters apply to left-justified sample pair mode as well as DSP serial mode, and MCE = 1, MFD = 0.

Max

7

Unit

ns

ns

DAI_P20–1

(SCLK)

DAI_P20–1

(FS)

DAI_P20–1

(DATA CHANNEL

A/B)

DAI_P20–1

(SCLK)

DAI_P20–1

(FS)

DAI_P20–1

(DATA CHANNEL

A/B)

DRIVE

EXTERNAL RECEIVE FS WITH MCE = 1, MFD = 0

SAMPLE

DRIVE

tSFSE/I

tHFSE/I

tDDTENFS

tHDTE/I

1ST BIT

tDDTE/I

tDDTLFSE

DRIVE

LATE EXTERNAL TRANSMIT FS

SAMPLE

DRIVE

tSFSE/I

tHFSE/I

tDDTENFS

tDDTLFSE

tHDTE/I

1ST BIT

tDDTE/I

Figure 22. External Late Frame Sync1

1 This figure reflects changes made to support left-justified sample pair mode.

2ND BIT

2ND BIT

Rev. G | Page 31 of 48 | December 2012