HI-8683 データシートの表示(PDF) - Holt Integrated Circuits

部品番号

コンポーネント説明

メーカー

HI-8683

Holt Integrated Circuits

HI-8683 Datasheet PDF : 10 Pages

| |||

HI-8683, HI-8684

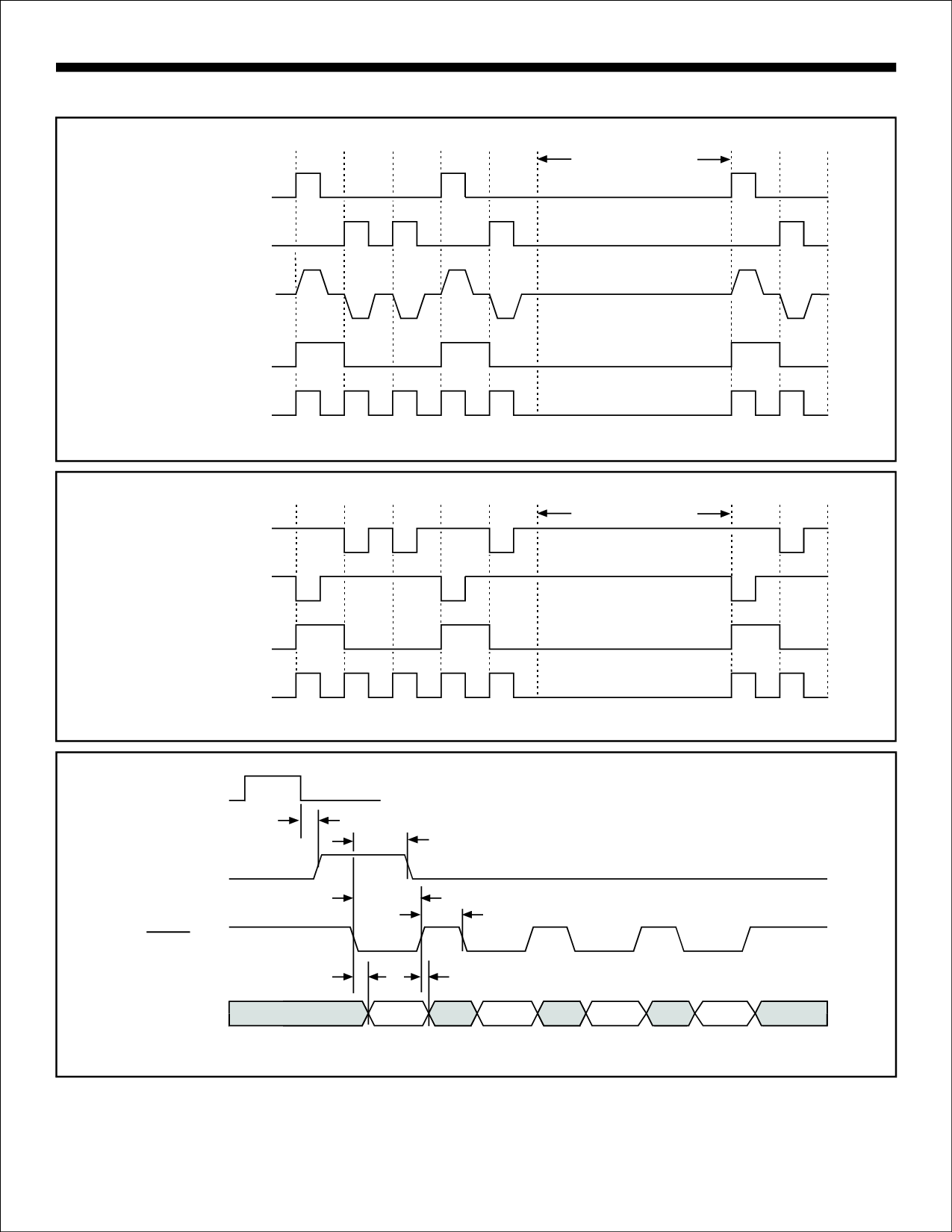

TIMING DIAGRAMS

INA (HI-8683 only)

ARINC Data Bits

28 29 30 31 32

Word Gap

4 Bit Periods Min.

INB (HI-8683 only)

VDIFF

RINA - RINB

(HI-8684 only)

DERIVED DATA

DERIVED CLOCK

FIGURE 3 - RECEIVER INPUT TIMING FOR ARINC 429

TESTA

TESTB

DERIVED DATA

DERIVED CLOCK

ARINC Data Bits

28 29 30 31 32

Word Gap

4 Bit Periods Min.

FIGURE 4 - TEST INPUT TIMING FOR ARINC 429

1

2

+5V

0V

+5V

0V

+10V

0V

-10V

1

2

+5V

0V

+5V

0V

DERIVED DATA

32nd

ARINC Bit

DATA RDY

READ

tDRDY

tRDYCLR

tRDPW

tRR

1st 8-bits

2nd 8-bits

D0 - D7

tRD

tFD

VALID

VALID

3rd 8-bits

VALID

4th 8-bits

VALID

FIGURE 5 - RECEIVER PARALLEL DATABUS TIMING

HOLT INTEGRATED CIRCUITS

5