White Electronic Designs => Micro Semi

WSF512K16-39G2C Hoja de datos - White Electronic Designs => Micro Semi

FEATURES

■ Access Times of 35ns (SRAM) and 90ns (FLASH)

■ Access Times of 70ns (SRAM) and 120ns (FLASH)

■ Packaging

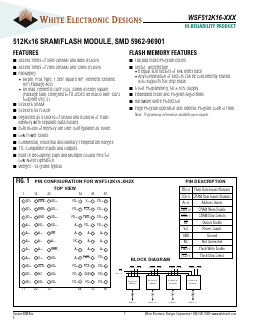

• 66 pin, PGA Type, 1.385" square HIP, Hermetic Ceramic HIP (Package 402)

• 68 lead, Hermetic CQFP (G2), 22mm (0.880") square (Package 500). Designed to fit JEDEC 68 lead 0.990” CQFJ footprint (Fig. 2)

■ 512Kx16 SRAM

■ 512Kx16 5V FLASH

■ Organized as 512Kx16 of SRAM and 512Kx16 of Flash Memory with separate Data Busses

■ Both blocks of memory are User Configurable as 1Mx8

■ Low Power CMOS

■ Commercial, Industrial and Military Temperature Ranges

■ TTL Compatible Inputs and Outputs

■ Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

■ Weight - 13 grams typical

FLASH MEMORY FEATURES

■ 100,000 Erase/Program Cycles

■ Sector Architecture

• 8 equal size sectors of 64K bytes each

• Any combination of sectors can be concurrently erased. Also supports full chip erase

■ 5 Volt Programming; 5V ± 10% Supply

■ Embedded Erase and Program Algorithms

■ Hardware Write Protection

■ Page Program Operation and Internal Program Control Time