Zentrum Mikroelektronik Dresden AG

UD61256 Hoja de datos - Zentrum Mikroelektronik Dresden AG

Description

Addressing

The UD61256 is a dynamic Write Read-memory with random access. FPM facilitates faster data operation with predefined row address. Via 9 address inputs the 18 address bits are transmitted into the internal address memories in a time-multiplex operation. The falling RAS edge takes over the row address. During RAS Low, the column address together with the CAS signal are taken over. The selection of one or more memory circuits can be made by activation of the RAS input.

Read-Write-Control

The choice between Read or Write cycle is made at the W input. HIGH at the W input causes a Read cycle, meanwhile LOW leads to a Write cycle.

Both CAS-controlled and W-control led Write cycles are possible with activated RAS signal.

FEATUREs

❐ Dynamic random access memory 262144 x 1 bit manufactured using a CMOS technology

❐ RAS access times 70 ns, 80 ns

❐ TTL-compatible

❐ Three-state output

❐ 256 refresh cycles 4 ms refresh cycle time

❐ FAST PAGE MODE

❐ Operating modes: Read, Write, Read - Write, RAS only Refresh, Hidden Refresh with address transfer

❐ Power Supply Voltage 5 V

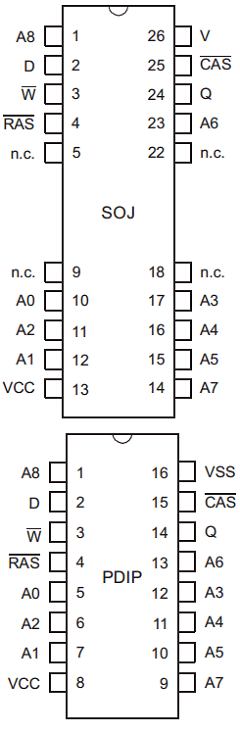

❐ Packages PDIP16 (300 mil) SOJ20/26 (300 mil)

❐ Operating temperature range 0 to 70 °C

❐ Quality assessment according to CECC 90000, CECC 90100 and CECC 90112