STMicroelectronics

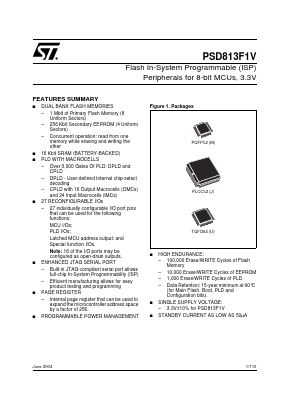

PSD813F1V-12UIT Hoja de datos - STMicroelectronics

SUMMARY DESCRIPTION

The PSD family of Programmable Microcontroller (MCU) Peripherals brings In-System Programmability (ISP) to Flash memory and programmable logic. The result is a simple and flexible solution for embedded designs. PSD devices combine many of the peripheral functions found in MCU based applications.

FEATURES SUMMARY

■ DUAL BANK FLASH MEMORIES

– 1 Mbit of Primary Flash Memory (8

Uniform Sectors)

– 256 Kbit Secondary EEPROM (4 Uniform

Sectors)

– Concurrent operation: read from one

memory while erasing and writing the

other

■ 16 Kbit SRAM (BATTERY-BACKED)

■ PLD WITH MACROCELLS

– Over 3,000 Gates Of PLD: DPLD and

CPLD

– DPLD - User-defined Internal chip-select

decoding

– CPLD with 16 Output Macrocells (OMCs)

and 24 Input Macrocells (IMCs)

■ 27 RECONFIGURABLE I/Os

– 27 individually configurable I/O port pins

that can be used for the following

functions:

MCU I/Os;

PLD I/Os;

Latched MCU address output; and

Special function I/Os.

Note: 16 of the I/O ports may be

configured as open-drain outputs.

■ ENHANCED JTAG SERIAL PORT

– Built-in JTAG-compliant serial port allows

full-chip In-System Programmability (ISP)

– Efficient manufacturing allows for easy

product testing and programming

■ PAGE REGISTER

– Internal page register that can be used to

expand the microcontroller address space

by a factor of 256.

■ PROGRAMMABLE POWER MANAGEMENT

■ HIGH ENDURANCE:

– 100,000 Erase/WRITE Cycles of Flash Memory

– 10,000 Erase/WRITE Cycles of EEPROM

– 1,000 Erase/WRITE Cycles of PLD

– Data Retention: 15-year minimum at 90°C

(for Main Flash, Boot, PLD and Configuration bits).

■ SINGLE SUPPLY VOLTAGE:

– 3.3V±10% for PSD813F1V

■ STANDBY CURRENT AS LOW AS 50µA