Zarlink Semiconductor Inc

MT9045AN Hoja de datos - Zarlink Semiconductor Inc

Description

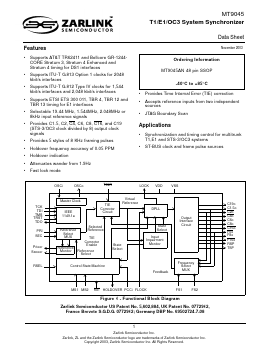

The MT9045 T1/E1/OC3 System Synchronizer contains a digital phase-locked loop (DPLL), which provides timing

and synchronization signals for multitrunk T1 and E1 primary rate transmission links and STS-3/OC3 links.

The MT9045 generates ST-BUS clock and framing signals that are phase locked to either a 19.44 MHz, 2.048MHz,

1.544MHz, or 8kHz input reference.

FEATUREs

• Supports AT&T TR62411 and Bellcore GR-1244-CORE Stratum 3, Stratum 4 Enhanced and Stratum 4 timing for DS1 interfaces

• Supports ITU-T G.813 Option 1 clocks for 2048 kbit/s interfaces

• Supports ITU-T G.812 Type IV clocks for 1,544 kbit/s interfaces and 2,048 kbit/s interfaces

• Supports ETSI ETS 300 011, TBR 4, TBR 12 and TBR 13 timing for E1 interfaces

• Selectable 19.44 MHz, 1.544MHz, 2.048MHz or 8kHz input reference signals

• Provides C1.5, C2, C4, C6, C8, C16, and C19 (STS-3/OC3 clock divided by 8) output clock signals

• Provides 5 styles of 8 KHz framing pulses

• Holdover frequency accuracy of 0.05 PPM

• Holdover indication

• Attenuates wander from 1.9Hz

• Fast lock mode

• Provides Time Interval Error (TIE) correction

• Accepts reference inputs from two independent sources

• JTAG Boundary Scan

APPLICATIONs

• Synchronization and timing control for multitrunk T1,E1 and STS-3/OC3 systems

• ST-BUS clock and frame pulse sources