Motorola => Freescale

MCM67C518 Hoja de datos - Motorola => Freescale

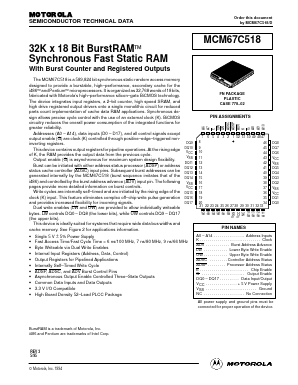

The MCM67C518 is a 589,824 bit synchronous static random access memory designed to provide a burstable, high–performance, secondary cache for the i486™ and Pentium™ microprocessors. It is organized as 32,768 words of 18 bits, fabricated with Motorola’s high–performance silicon–gate BiCMOS technology.

This device is ideally suited for systems that require wide data bus widths and cache memory. See Figure 2 for applications information.

• Single 5 V ± 5% Power Supply

• Fast Access Time/Fast Cycle Time = 6 ns/100 MHz, 7 ns/80 MHz, 9 ns/66 MHz

• Byte Writeable via Dual Write Enables

• Internal Input Registers (Address, Data, Control)

• Output Registers for Pipelined Applications

• Internally Self–Timed Write Cycle

• ADSP, ADSC, and ADV Burst Control Pins

• Asynchronous Output Enable Controlled Three–State Outputs

• Common Data Inputs and Data Outputs

• 3.3 V I/O Compatible

• High Board Density 52–Lead PLCC Package