Integrated Device Technology

IDT79R305240J Hoja de datos - Integrated Device Technology

INTRODUCTION

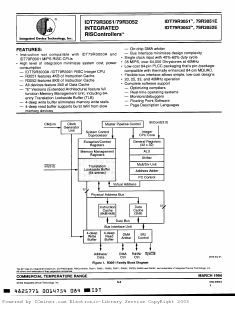

The IDT IDT79R3051 family is a series of high-performance 32-bit microprocessors featuring a high level of integration which are targeted to high-performance, but costsensitive embedded processing applications. The IDT79R3051 family is designed to bring the high-performance inherent in the MIPS RISC architecture into low-cost, simplified, power-sensitive applications.

FEATURES:

• Instruction set compatible with IDT79R3000A and IDT79R3001 MIPS RISC CPUs

• High level of integration minimizes system cost, power consumption

— IDT79R3000A /IDT79R3001 RISC Integer CPU

— R3051 features 4KB of Instruction Cache

— R3052 features 8KB of Instruction Cache

— All devices feature 2kB of Data Cache

— “E” Versions (Extended Architecture) feature full function Memory Management Unit, including 64- entry Translation Lookaside Buffer (TLB)

— 4-deep write buffer eliminates memory write stalls

— 4-deep read buffer supports burst refill from slow memory devices

— On-chip DMA arbiter

— Bus Interface minimizes design complexity

• Single clock input with 40%-60% duty cycle

• 35 MIPS, over 64,000 Dhrystones at 40MHz

• Low-cost 84-pin PLCC packaging thats pin-/packagecompatible with thermally enhanced 84-pin MQUAD.

• Flexible bus interface allows simple, low-cost designs

• 20, 25, 33, and 40MHz operation

• Complete software support

— Optimizing compilers

— Real-time operating systems

— Monitors/debuggers

— Floating Point Software

— Page Description Languages