ETC

FS612509-01 Hoja de datos - ETC

[AMI]

Description

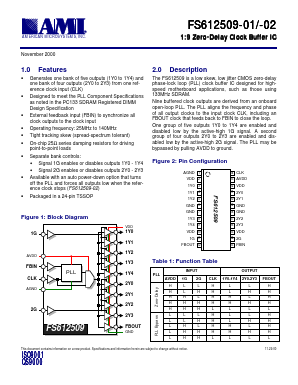

The FS612509 is a low skew, low jitter CMOS zero-delay phase-lock loop (PLL) clock buffer IC designed for highspeed motherboard applications, such as those using 133MHz SDRAM.

Nine buffered clock outputs are derived from an onboard open-loop PLL. The PLL aligns the frequency and phase of all output clocks to the input clock CLK, including an FBOUT clock that feeds back to FBIN to close the loop.

FEATUREs

• Generates one bank of five outputs (1Y0 to 1Y4) and one bank of four outputs (2Y0 to 2Y3) from one reference clock input (CLK)

• Designed to meet the PLL Component Specifications as noted in the PC133 SDRAM Registered DIMM Design Specification

• External feedback input (FBIN) to synchronize all clock outputs to the clock input

• Operating frequency: 25MHz to 140MHz

• Tight tracking skew (spread-spectrum tolerant)

• On-chip 25Ω series damping resistors for driving point-to-point loads

• Separate bank controls:

♦ Signal 1G enables or disables outputs 1Y0 - 1Y4

♦ Signal 2G enables or disables outputs 2Y0 - 2Y3

• Available with an auto power-down option that turns off the PLL and forces all outputs low when the reference clock stops (FS612509-02)

• Packaged in a 24-pin TSSOP