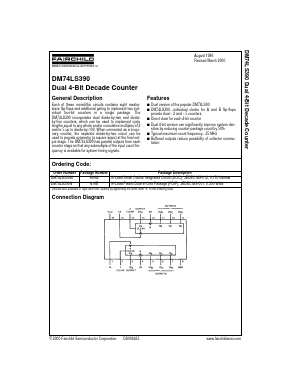

Fairchild Semiconductor

DM74LS390MX Hoja de datos - Fairchild Semiconductor

General Description

Each of these monolithic circuits contains eight master-slave flip-flops and additional gating to implement two individual four-bit counters in a single package. The DM74LS390 incorporates dual divide-by-two and divideby-five counters, which can be used to implement cycle lengths equal to any whole and/or cumulative multiples of 2 and/or 5 up to divide-by-100. When connected as a bi-quinary counter, the separate divide-by-two circuit can be used to provide symmetry (a square wave) at the final output stage. The DM74LS390 has parallel outputs from each counter stage so that any submultiple of the input count frequency is available for system-timing signals.

FEATUREs

■ Dual version of the popular DM74LS90

■ DM74LS390...individual clocks for A and B flip-flops provide dual ÷ 2 and ÷ 5 counters

■ Direct clear for each 4-bit counter

■ Dual 4-bit version can significantly improve system densities by reducing counter package count by 50%

■ Typical maximum count frequency...35 MHz

■ Buffered outputs reduce possibility of collector commutation