Cypress Semiconductor

CY7C453 Hoja de datos - Cypress Semiconductor

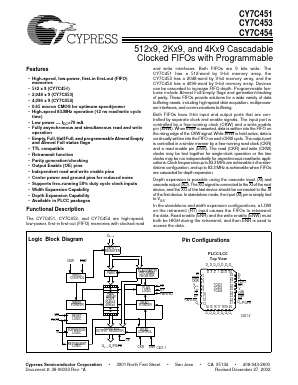

Functional Description

The CY7C451, CY7C453, and CY7C454 are high-speed, low-power, first-in first-out (FIFO) memories with clocked read and write interfaces. Both FIFOs are 9 bits wide. The CY7C451 has a 512-word by 9-bit memory array, the CY7C453 has a 2048-word by 9-bit memory array, and the CY7C454 has a 4096-word by 9-bit memory array. Devices can be cascaded to increase FIFO depth. Programmable features include Almost Full/Empty flags and generation/checking of parity. These FIFOs provide solutions for a wide variety of data buffering needs, including high-speed data acquisition, multiprocessor interfaces, and communications buffering.

FEATUREs

• High-speed, low-power, first-in first-out (FIFO) memories

• 512 x 9 (CY7C451)

• 2,048 x 9 (CY7C453)

• 4,096 x 9 (CY7C454)

• 0.65 micron CMOS for optimum speed/power

• High-speed 83-MHz operation (12 ns read/write cycle time)

• Low power — ICC=70 mA

• Fully asynchronous and simultaneous read and write operation

• Empty, Full, Half Full, and programmable Almost Empty and Almost Full status flags

• TTL compatible

• Retransmit function

• Parity generation/checking

• Output Enable (OE) pins

• Independent read and write enable pins

• Center power and ground pins for reduced noise

• Supports free-running 50% duty cycle clock inputs

• Width Expansion Capability

• Depth Expansion Capability

• Available in PLCC packages