Alliance Semiconductor

AS29LV160B Hoja de datos - Alliance Semiconductor

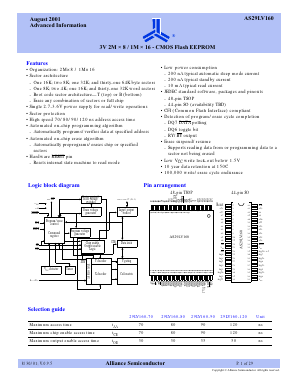

Features

• Organization: 2M×8 / 1M×16

• Sector architecture

- One 16K; two 8K; one 32K; and thirty-one 64K byte sectors

- One 8K; two 4K; one 16K; and thirty-one 32K word sectors

- Boot code sector architecture—T (top) or B (bottom)

- Erase any combination of sectors or full chip

• Single 2.7-3.6V power supply for read/write operations

• Sector protection

• High speed 70/80/90/120 ns address access time

• Automated on-chip programming algorithm

- Automatically programs/verifies data at specified address

• Automated on-chip erase algorithm

- Automatically preprograms/erases chip or specified sectors

• Hardware RESET pin

- Resets internal state machine to read mode

• Low power consumption

- 200 nA typical automatic sleep mode current

- 200 nA typical standby current

- 10 mA typical read current

• JEDEC standard software, packages and pinouts

- 48-pin TSOP

- 44-pin SO (availability TBD)

• CFI (Common Flash Interface) compliant

• Detection of program/erase cycle completion

- DQ7 DATA polling

- DQ6 toggle bit

- RY/BY output

• Erase suspend/resume

- Supports reading data from or programming data to a sector not being erased

• Low VCC write lock-out below 1.5V

• 10 year data retention at 150C

• 100,000 write/erase cycle endurance