Analog Devices

ADSP-2188M Hoja de datos - Analog Devices

GENERAL DESCRIPTION

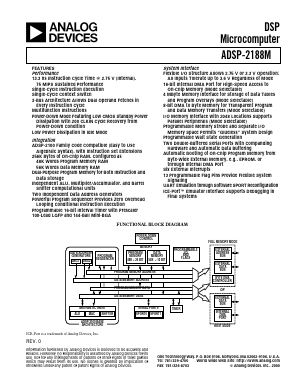

The ADSP-2188M is a single-chip microcomputer optimized for digital signal processing (DSP) and other high-speed numeric processing applications.

The ADSP-2188M combines the ADSP-2100 family base architecture (three computational units, data address generators, and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory.

FEATURES

Performance

13.3 ns Instruction Cycle Time @ 2.75 V (Internal),

75 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

3-Bus Architecture Allows Dual Operand Fetches in

Every Instruction Cycle

Multifunction Instructions

Power-Down Mode Featuring Low CMOS Standby Power

Dissipation with 200 CLKIN Cycle Recovery from

Power-Down Condition

Low Power Dissipation in Idle Mode

Integration

ADSP-2100 Family Code Compatible (Easy to Use

Algebraic Syntax), with Instruction Set Extensions

256K Bytes of On-Chip RAM, Configured as

48K Words Program Memory RAM

56K Words Data Memory RAM

Dual-Purpose Program Memory for Both Instruction and

Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel

Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides Zero Overhead

Looping Conditional Instruction Execution

Programmable 16-Bit Interval Timer with Prescaler

100-Lead LQFP and 144-Ball Mini-BGA

System Interface

Flexible I/O Structure Allows 2.75 V or 3.3 V Operation;

All Inputs Tolerate up to 3.6 V Regardless of Mode

16-Bit Internal DMA Port for High-Speed Access to

On-Chip Memory (Mode Selectable)

4 MByte Memory Interface for Storage of Data Tables

and Program Overlays (Mode Selectable)

8-Bit DMA to Byte Memory for Transparent Program

and Data Memory Transfers (Mode Selectable)

I/O Memory Interface with 2048 Locations Supports

Parallel Peripherals (Mode Selectable)

Programmable Memory Strobe and Separate I/O

Memory Space Permits “Glueless” System Design

Programmable Wait State Generation

Two Double-Buffered Serial Ports with Companding

Hardware and Automatic Data Buffering

Automatic Booting of On-Chip Program Memory from

Byte-Wide External Memory, e.g., EPROM, or

through Internal DMA Port

Six External Interrupts

13 Programmable Flag Pins Provide Flexible System

Signaling

UART Emulation through Software SPORT Reconfiguration

ICE-Port™ Emulator Interface Supports Debugging in

Final Systems