Analog Devices

ADN2865ACP-RL7 Hoja de datos - Analog Devices

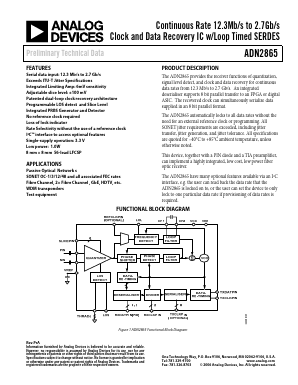

PRODUCT DESCRIPTION

The ADN2865 provides the receiver functions of quantization, signal level detect, and clock and data recovery for continuous data rates from 12.3 Mb/s to 2.7 Gb/s. An integrated deserialiser supports 8 bit parallel transfer to an FPGA or digital ASIC. The recovered clock can simultaneously serialize data supplied in an 8 bit parallel format.

FEATURES

Serial data input: 12.3 Mb/s to 2.7 Gb/s

Exceeds ITU-T Jitter Specifications

Integrated Limiting Amp: 6mV sensitivity

Adjustable slice level: ±100 mV

Patented dual-loop clock recovery architecture

Programmable LOS detect and Slice Level

Integrated PRBS Generator and Detector

No reference clock required

Loss of lock indicator

Rate Selectivity without the use of a reference clock

I2C™ interface to access optional features

Single-supply operation: 3.3 V

Low power: 1.0W

8 mm × 8 mm 56-lead LFCSP

APPLICATIONS

Passive Optical Network s

SONET OC-1/3/12/48 and all associated FEC rates

Fibre Channel, 2× Fibre Channel , GbE, HDTV, etc.

WDM transponders

Test equipment