Analog Devices

AD9250 Hoja de datos - Analog Devices

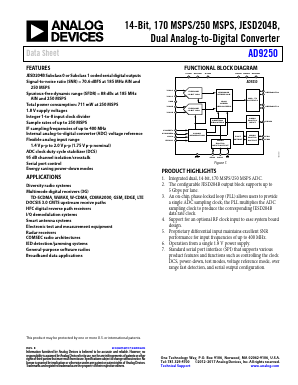

GENERAL DESCRIPTION

The AD9250 is a dual, 14-bit ADC with sampling speeds of up to 250 MSPS. The AD9250 is designed to support communications applications where low cost, small size, wide bandwidth, and versatility are desired.

FEATURES

JESD204B Subclass 0 or Subclass 1 coded serial digital outputs

Signal-to-noise ratio (SNR) = 70.6 dBFS at 185 MHz AIN and

250 MSPS

Spurious-free dynamic range (SFDR) = 88 dBc at 185 MHz

AIN and 250 MSPS

Total power consumption: 711 mW at 250 MSPS

1.8 V supply voltages

Integer 1-to-8 input clock divider

Sample rates of up to 250 MSPS

IF sampling frequencies of up to 400 MHz

Internal analog-to-digital converter (ADC) voltage reference

Flexible analog input range

1.4 V p-p to 2.0 V p-p (1.75 V p-p nominal)

ADC clock duty cycle stabilizer (DCS)

95 dB channel isolation/crosstalk

Serial port control

Energy saving power-down modes

APPLICATIONS

Diversity radio systems

Multimode digital receivers (3G)

TD-SCDMA, WiMAX, W-CDMA, CDMA2000, GSM, EDGE, LTE

DOCSIS 3.0 CMTS upstream receive paths

HFC digital reverse path receivers

I/Q demodulation systems

Smart antenna systems

Electronic test and measurement equipment

Radar receivers

COMSEC radio architectures

IED detection/jamming systems

General-purpose software radios

Broadband data applications