Integrated Device Technology

9173B-15CS08LFT Hoja de datos - Integrated Device Technology

Description

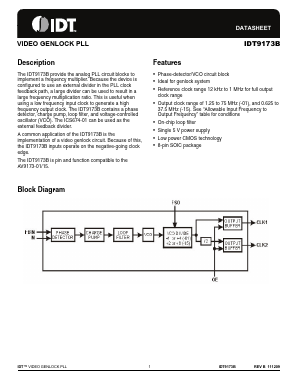

The IDT9173B provide the analog PLL circuit blocks to implement a frequency multiplier. Because the device is configured to use an external divider in the PLL clock feedback path, a large divider can be used to result in a large frequency multiplication ratio. This is useful when using a low frequency input clock to generate a high frequency output clock. The IDT9173B contains a phase detector, charge pump, loop filter, and voltage-controlled oscillator (VCO). The ICS674-01 can be used as the external feedback divider.

FEATUREs

• Phase-detector/VCO circuit block

• Ideal for genlock system

• Reference clock range 12 kHz to 1 MHz for full output clock range

• Output clock range of 1.25 to 75 MHz (-01), and 0.625 to 37.5 MHz (-15). See “Allowable Input Frequency to Output Frequency” table for conditions

• On-chip loop filter

• Single 5 V power supply

• Low power CMOS technology

• 8-pin SOIC package