Renesas Electronics

5962F9672101VXC Hoja de datos - Renesas Electronics

Description

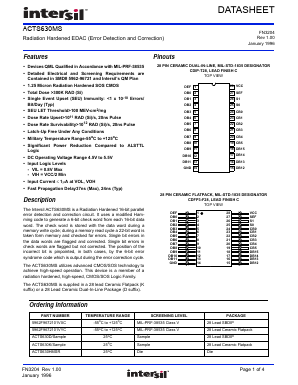

The Intersil ACTS630MS is a Radiation Hardened 16-bit parallel error detection and correction circuit. It uses a modified Hamming code to generate a 6-bit check word from each 16-bit data word. The check word is stored with the data word during a memory write cycle; during a memory read cycle a 22-bit word is taken form memory and checked for errors. Single bit errors in the data words are flagged and corrected. Single bit errors in check words are flagged but not corrected. The position of the incorrect bit is pinpointed, in both cases, by the 6-bit error syndrome code which is output during the error correction cycle.

FEATUREs

• Devices QML Qualified in Accordance with MIL-PRF-38535

• Detailed Electrical and Screening Requirements are

Contained in SMD# 5962-96721 and Intersil’s QM Plan

• 1.25 Micron Radiation Hardened SOS CMOS

• Total Dose >300K RAD (Si)

• Single Event Upset (SEU) Immunity: <1 x 10-10 Errors/

Bit/Day (Typ)

• SEU LET Threshold>100 MEV-cm2/mg

• Dose Rate Upset>1011 RAD (Si)/s, 20ns Pulse

• Dose Rate Survivability>1012 RAD (Si)/s, 20ns Pulse

• Latch-Up Free Under Any Conditions

• Military Temperature Range-55°C to +125°C

• Significant Power Reduction Compared to ALSTTL

Logic

• DC Operating Voltage Range 4.5V to 5.5V

• Input Logic Levels

- VIL = 0.8V Max

- VIH = VCC/2 Min

• Input Current ≤ 1μA at VOL, VOH

• Fast Propagation Delay37ns (Max), 24ns (Typ)