AMI Semiconductor

11920-201 Hoja de datos - AMI Semiconductor

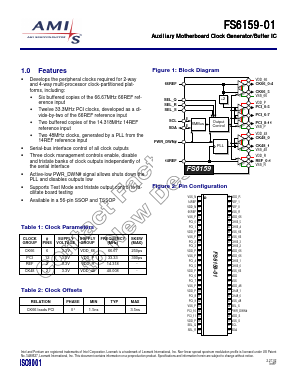

Features

• Develops the peripheral clocks required for 2-way and 4-way multi-processor clock-partitioned platforms, including:

♦ Six buffered copies of the 66.67MHz 66REF reference input

♦ Twelve 33.3MHz PCI clocks, developed as a divide-by-two of the 66REF reference input

♦ Two buffered copies of the 14.318MHz 14REF reference input

♦ Two 48MHz clocks, generated by a PLL from the 14REF reference input

• Serial-bus interface control of all clock outputs

• Three clock management controls enable, disable and tristate banks of clock outputs independently of the serial interface

• Active-low PWR_DWN# signal allows shuts down the PLL and disables outputs low

• Supports Test Mode and tristate output control to facilitate board testing

• Available in a 56-pin SSOP and TSSOP