UT54ACS109E Ver la hoja de datos (PDF) - Aeroflex Corporation

Número de pieza

componentes Descripción

fabricante

UT54ACS109E Datasheet PDF : 10 Pages

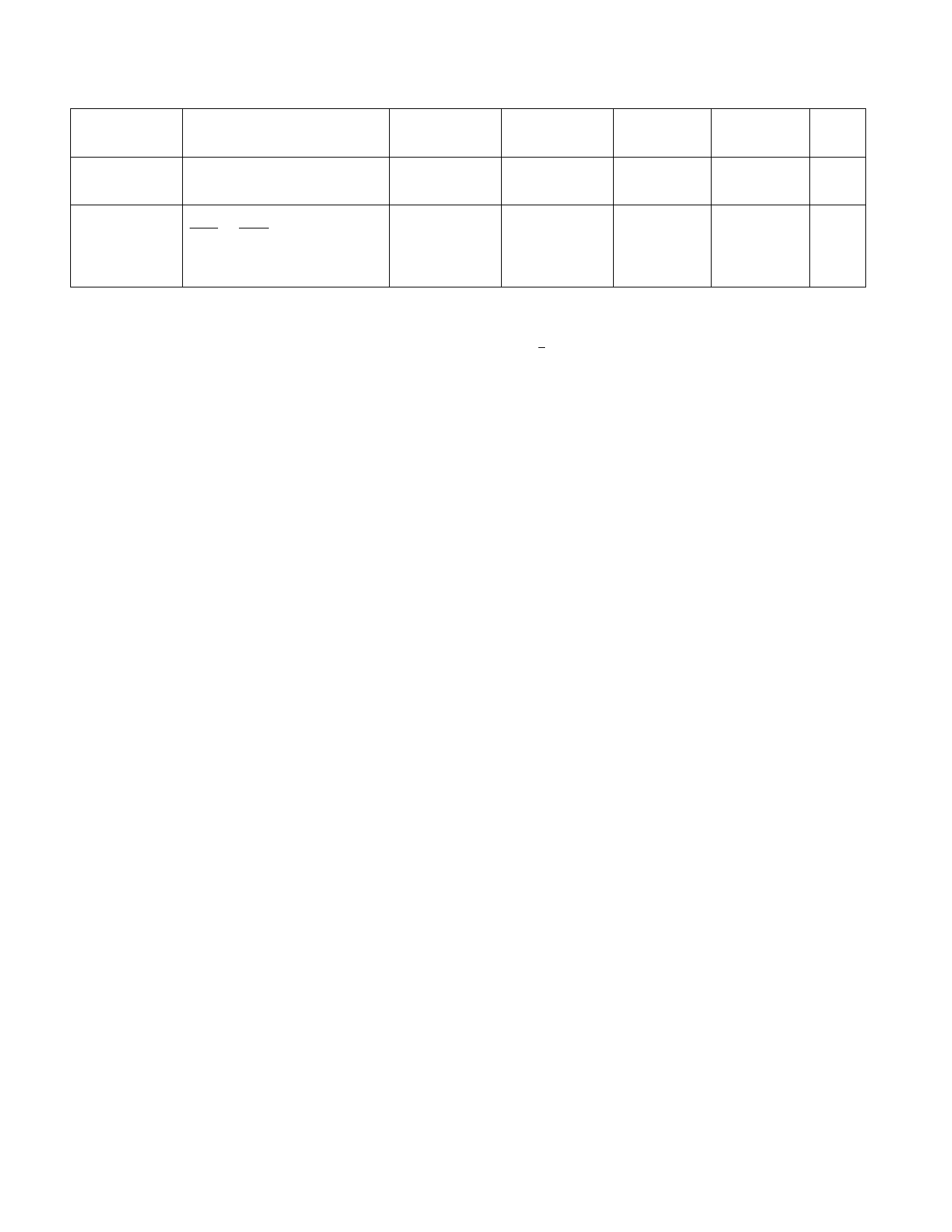

| |||

tSU2

Data setup time before CLK ↑ CL = 50pF 3.0V, 4.5V, and

5

ns

5.5V

tH3

Data hold time after CLK ↑

CL = 50pF 3.0V, 4.5V, and

5.5V

3

ns

tW

Minimum pulse width

CL = 50pF 3.0V, 4.5V, and

8

ns

PRE or CLR low

5.5V

CLK high

CLK low

Notes:

1. Maximum allowable relative shift equals 50mV.

2. All specifications valid for radiation dose ≤ 1E6 rads(Si) per MIL-STD-883 Method 1019 Condition A and section 3.11.2.

3. Based on characterization, hold time (tH) of 0ns can be assumed if data setup time (tSU2) is >10ns. This is guaranteed, but not tested.

4. Historically maximum frequency "fMAX" was based off minimum pulse width (tW), fMAX = 1/2tW. In practice, the achievable fMAX is dictated by the CLK to Q

propagation delays listed in the AC electrical table. For a more complete description on calculating the applicable fMAX reference, the application note titled

“Frequency vs Load Capacitance for the MSI Product Family" is located at www.aeroflex.com/

6