74LVT640DB Ver la hoja de datos (PDF) - NXP Semiconductors.

Número de pieza

componentes Descripción

fabricante

74LVT640DB Datasheet PDF : 15 Pages

| |||

Nexperia

74LVT640

3.3 V Octal transceiver with direction pin; inverting; 3-state

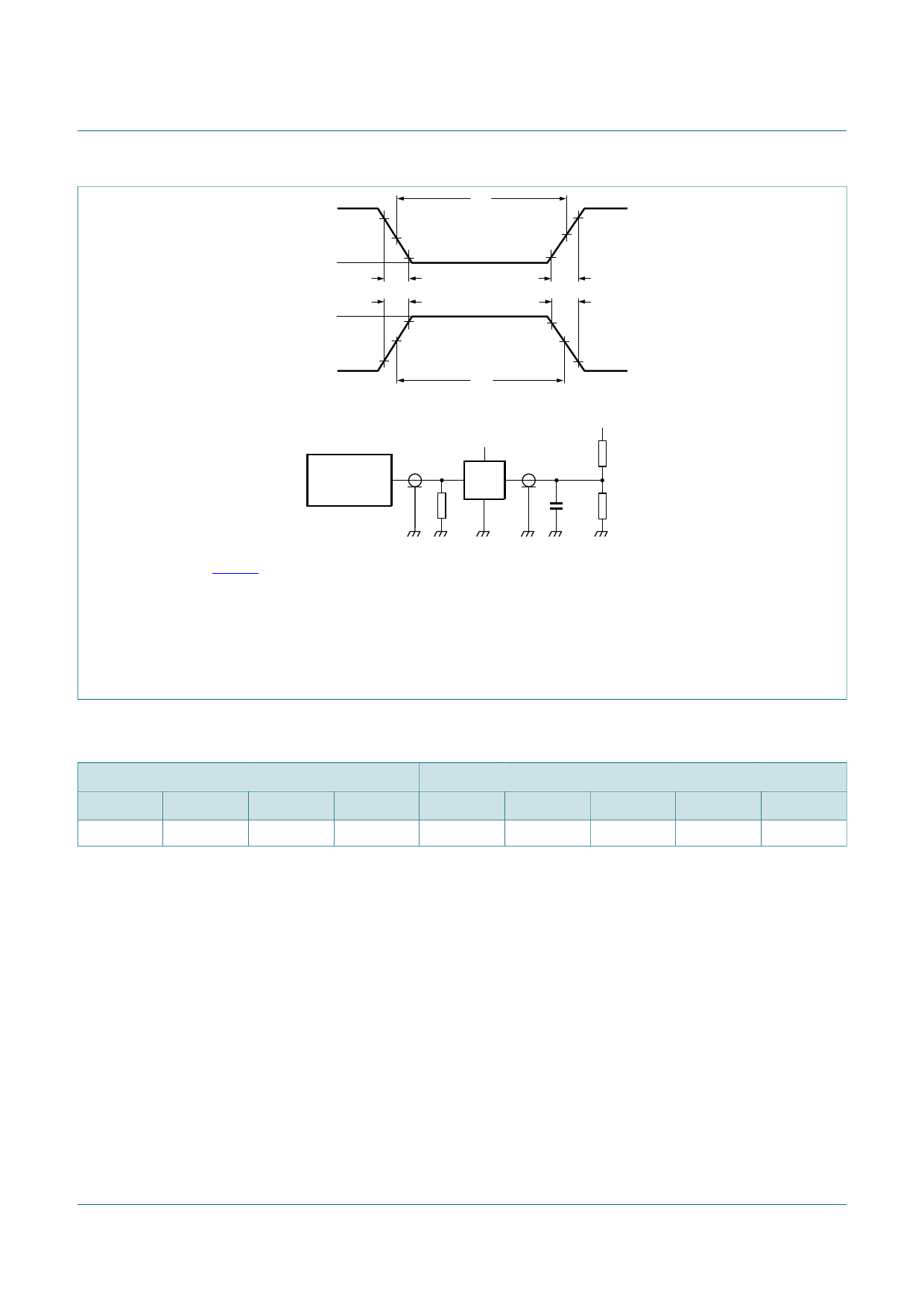

VI 90 %

tW

negative

pulse

VM

10 %

0V

tf

VI

positive

pulse

tr

90 %

VM

10 %

0V

tW

VM

tr

tf

VM

VCC

VI

PULSE

GENERATOR

VO

DUT

RT

VEXT

RL

CL

RL

001aae235

Test data is given in Table 9.

Definitions test circuit:

RL = Load resistance;

CL = Load capacitance including jig and probe capacitance;

RT = Termination resistance should be equal to output impedance Zo of the pulse generator;

VEXT = External voltage for measuring switching times.

Figure 7. Test circuit for switching times

Table 9. Test data

Input

VI

2.7 V

fi

≤ 10 MHz

tW

500 ns

tr, tf

≤ 2.5 ns

Load

RL

500 Ω

CL

50 pF

VEXT

tPHZ, tPZH

GND

tPLZ, tPZL

6V

tPLH, tPHL

open

74LVT640

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 3 — 10 April 2017

© Nexperia B.V. 2017. All rights reserved.

8 / 15