DSP56362UM Ver la hoja de datos (PDF) - Freescale Semiconductor

Número de pieza

componentes Descripción

fabricante

DSP56362UM Datasheet PDF : 152 Pages

| |||

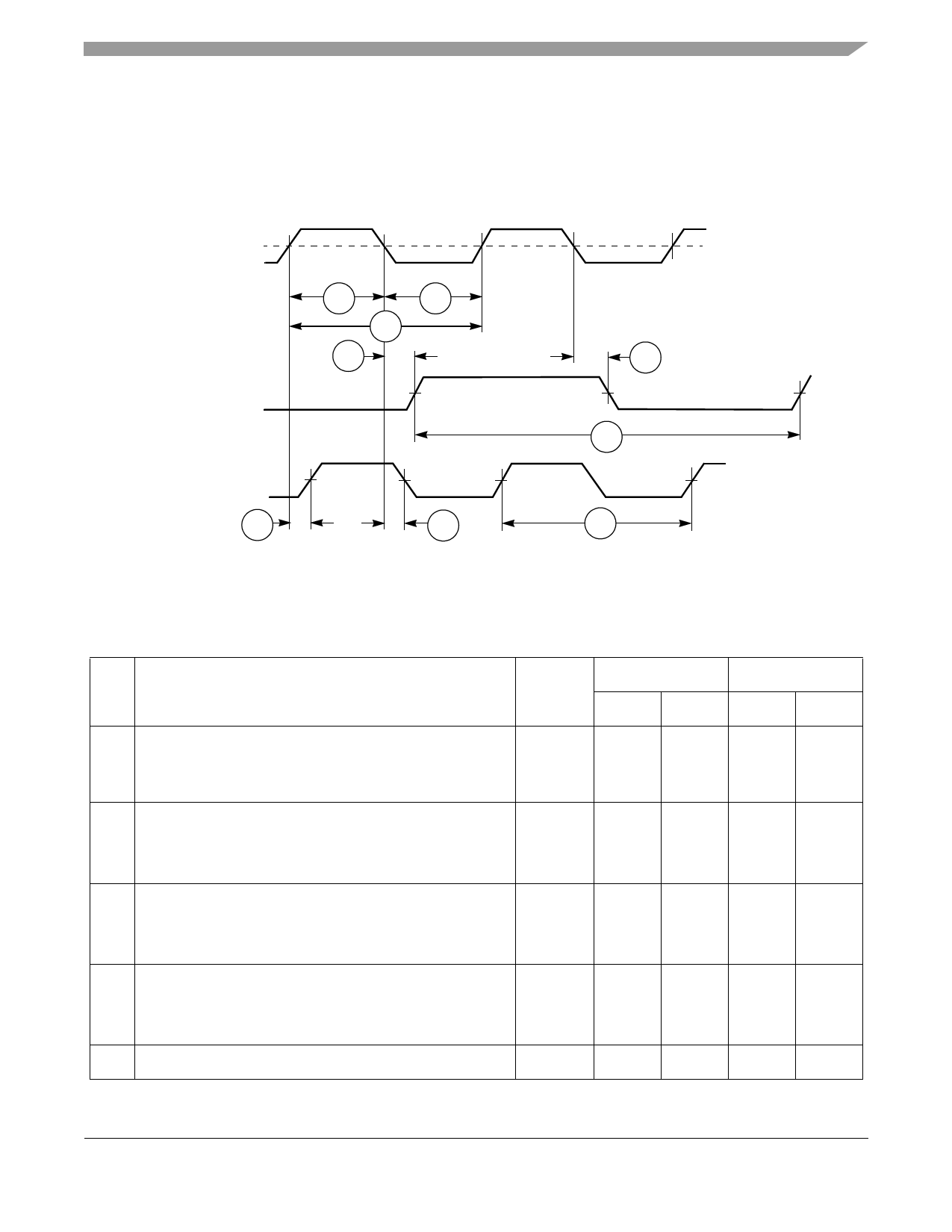

EXTERNAL CLOCK OPERATION

3.7 EXTERNAL CLOCK OPERATION

The DSP56362 system clock is an externally supplied square wave voltage source connected to EXTAL

(Figure 3-1)

EXTAL

VILC ETH 2

5

CLKOUT With

PLL Disabled

ETL

3

4

ETC

CLKOUT With

PLL Enabled

Midpoint

VIHC

5

7

6a

6b

7

Note: The midpoint is 0.5 (VIHC + VILC).

Figure 3-1 External Clock Timing

AA0459

Table 3-5 Clock Operation 100 and 120 MHz Values

No.

Characteristics

Symbol

100 MHz

Min

Max

120 MHz

Min

Max

1 Frequency of EXTAL (EXTAL Pin Frequency)

The rise and fall time of this external clock should be 3 ns

maximum.

2 EXTAL input high1, 2

• With PLL disabled (46.7%–53.3% duty cycle)3

• With PLL enabled (42.5%–57.5% duty cycle)3

3 EXTAL input low1, 2

• With PLL disabled (46.7%–53.3% duty cycle)3

• With PLL enabled (42.5%–57.5% duty cycle)3

4 EXTAL cycle time2

• With PLL disabled

• With PLL enabled

Ef

0

100.0

0

120.0

ETH

4.67 ns

∞

0.00 ns

∞

4.25 ns 157.0 µs 0.00 ns 157.0 µs

ETL

4.67 ns

∞

4.67 ns

—

4.25 ns 157.0 µs 4.25 ns 1570.00

ETC

10.00 ns ∞

8.33 ns

—

10.00 ns 273.1 µs 8.33 ns 273.1 µs

5 CLKOUT change from EXTAL fall with PLL disabled

4.3 ns 11.0 ns

DSP56362 Technical Data, Rev. 4

Freescale Semiconductor

3-5