AD9739A(Rev0) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

fabricante

AD9739A Datasheet PDF : 44 Pages

| |||

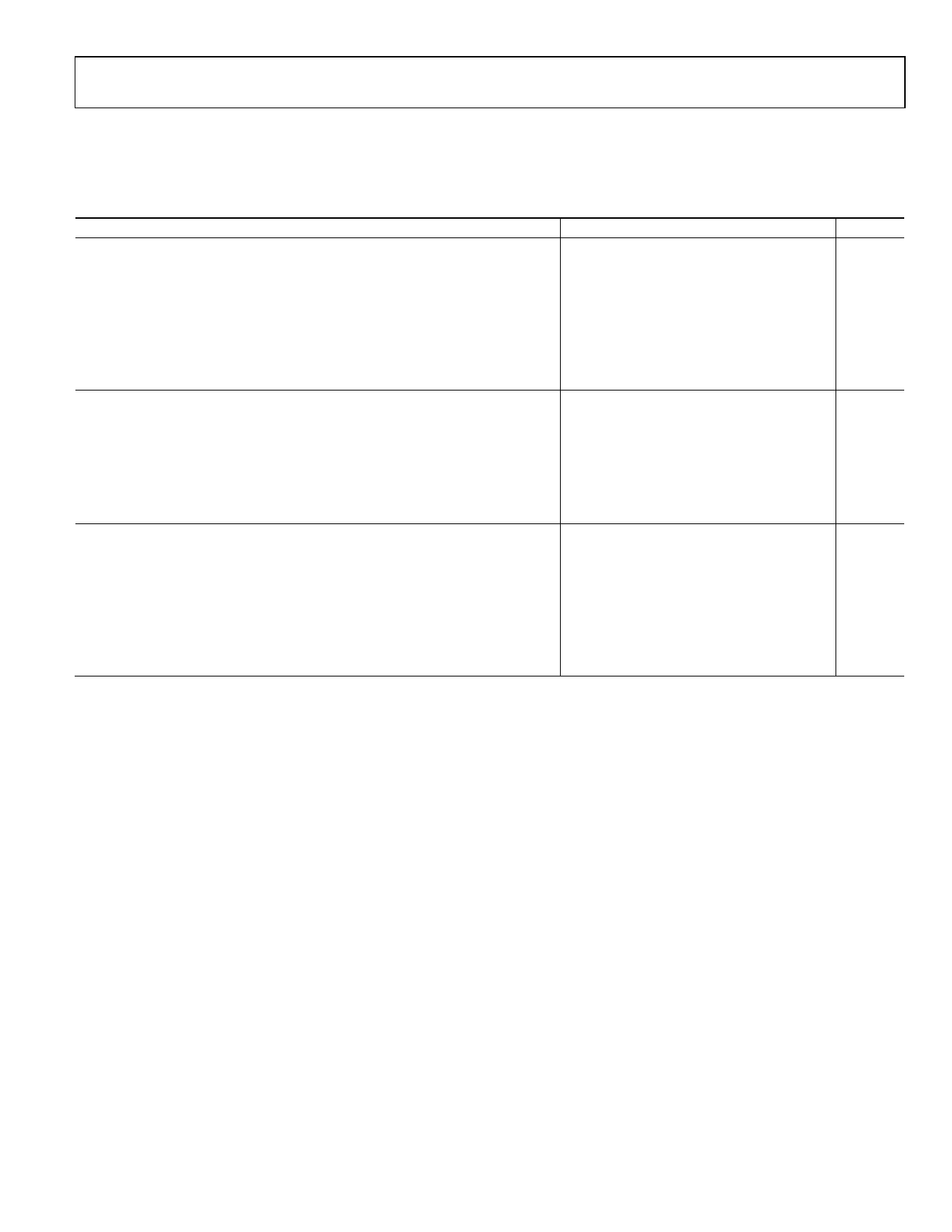

SERIAL PORT SPECIFICATIONS

VDDA = VDD33 = 3.3 V ± 6%, VDDC = VDD = 1.8 V ± 6%.

Table 3.

Parameter

WRITE OPERATION (See Figure 71)

SCLK Clock Rate, fSCLK, 1/tSCLK

SCLK Clock High, tHI

SCLK Clock Low, tLOW

SDIO to SCLK Setup Time, tDS

SCLK to SDIO Hold Time, tDH

CS to SCLK Setup Time, tS

SCLK to CS Hold Time, tH

READ OPERATION (See Figure 72 and Figure 73)

SCLK Clock Rate, fSCLK, 1/tSCLK

SCLK Clock High, tHI

SCLK Clock Low, tLOW

SDIO to SCLK Setup Time, tDS

SCLK to SDIO Hold Time, tDH

CS to SCLK Setup Time, tS

SCLK to SDIO (or SDO) Data Valid Time, tDV

CS to SDIO (or SDO) Output Valid to High-Z, tEZ

INPUTS (SDI, SDIO, SCLK, CS)

Voltage in High, VIH

Voltage in Low, VIL

Current in High, IIH

Current in Low, IIL

OUTPUT (SDIO)

Voltage Out High, VOH

Voltage Out Low, VOL

Current Out High, IOH

Current Out Low, IOL

AD9739A

Min

Typ

Max Unit

20

MHz

18

ns

18

ns

2

ns

1

ns

3

ns

2

ns

18

18

2

1

3

2

20

MHz

ns

ns

ns

ns

ns

15

ns

ns

2.0

3.3

0

−10

−10

2.4

0

4

4

V

0.8

V

+10 μA

+10 μA

3.5

V

0.4

V

mA

mA

Rev. 0 | Page 5 of 44