AT45DB321-TC Ver la hoja de datos (PDF) - Atmel Corporation

Número de pieza

componentes Descripción

fabricante

AT45DB321-TC Datasheet PDF : 21 Pages

| |||

AT45DB321

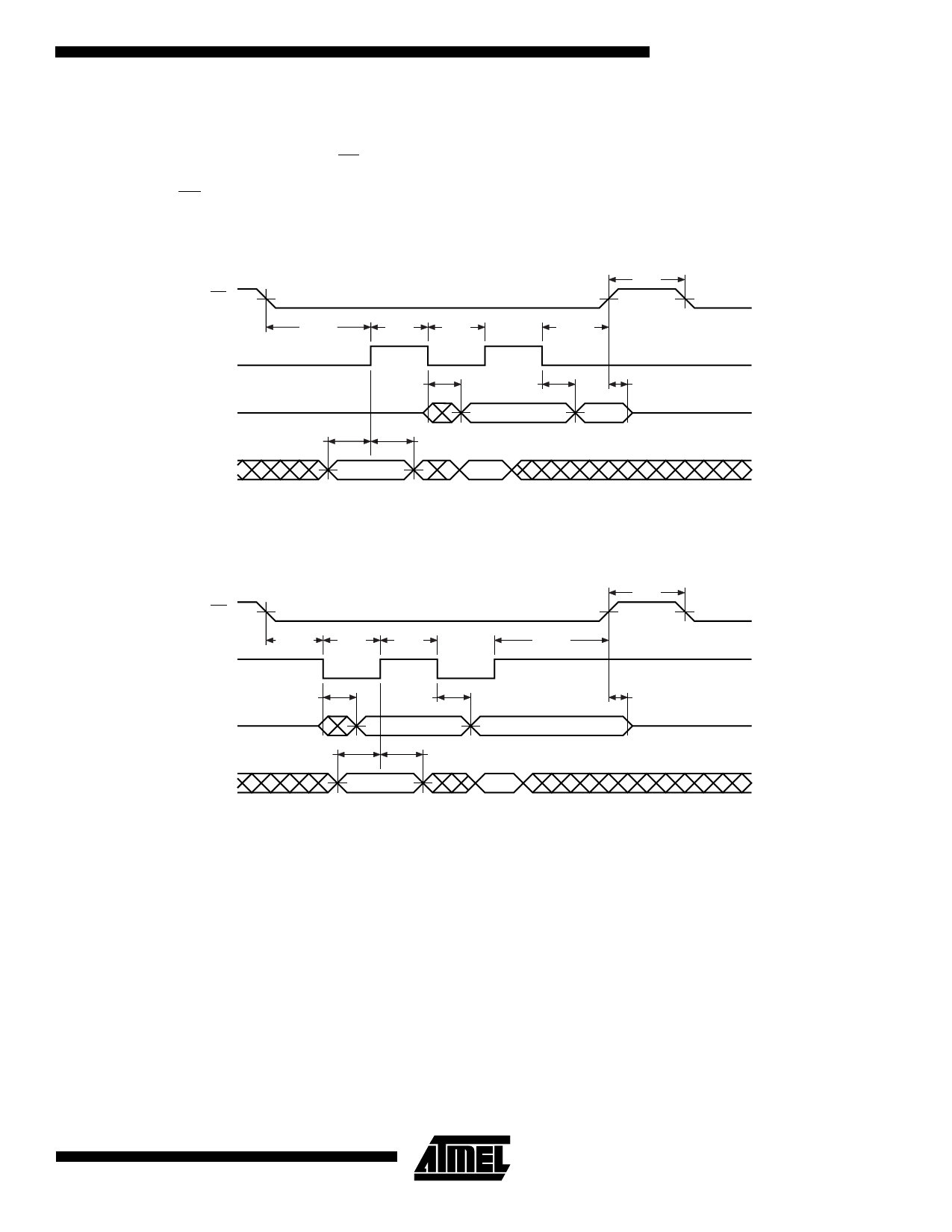

AC Waveforms

Two different timing diagrams are shown below. Waveform

1 shows the SCK signal being low when CS makes a high-

to-low transition, and Waveform 2 shows the SCK signal

being high when CS makes a high-to-low transition. Both

waveforms show valid timing diagrams. The setup and hold

Waveform 1 – Inactive Clock Polarity Low

times for the SI signal are referenced to the low-to-high

transition on the SCK signal.

Waveform 1 shows timing that is also compatible with SPI

Mode 0, and Waveform 2 shows timing that is compatible

with SPI Mode 3.

tCS

CS

tCSS

tWH tWL

tCSH

SCK

tV

HIGH IMPEDANCE

SO

tHO

VALID OUT

tDIS

HIGH IMPEDANCE

tSU

tH

SI

VALID IN

Waveform 2 – Inactive Clock Polarity High

CS

SCK

SO

SI

tCSS tWL tWH

tV

HIGH Z

tSU

tHO

VALID OUT

tH

VALID IN

tCSH

tCS

tDIS

HIGH IMPEDANCE

9