M38C85M6-FP Ver la hoja de datos (PDF) - MITSUBISHI ELECTRIC

Número de pieza

componentes Descripción

fabricante

M38C85M6-FP Datasheet PDF : 51 Pages

| |||

PRELIMINARY NSocothimcaene:gpTeah.riasmisetnrioct laimfiintsalasrepescuibfijceacttioton.

MITSUBISHI MICROCOMPUTERS

38C8 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

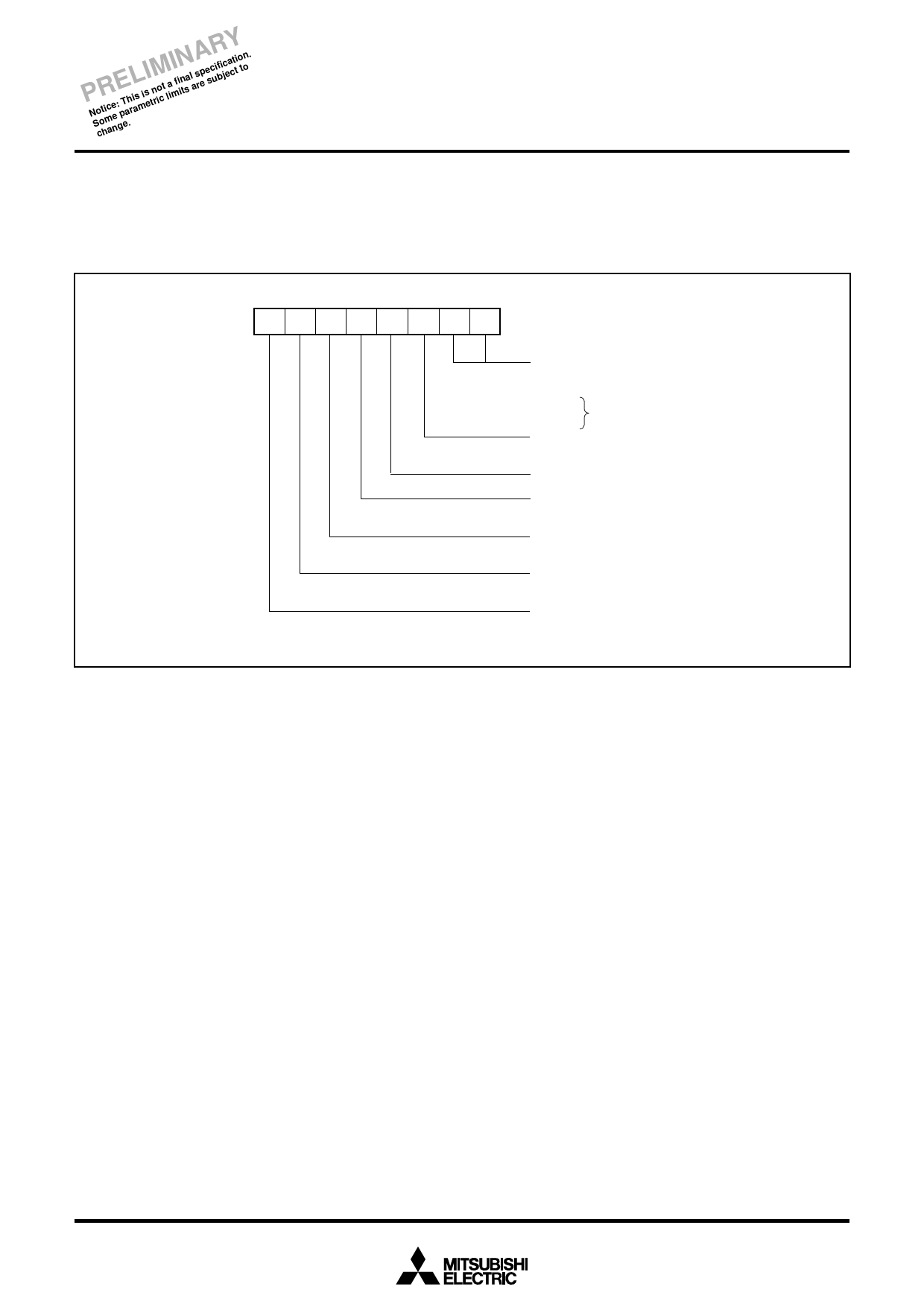

[CPU Mode Register (CPUM)] 003B16

The CPU mode register contains the stack page selection bit and the

internal system clock selection bit.

The CPU mode register is allocated at address 003B16.

b7

Fig. 7 Structure of CPU mode register

b0

CPU mode register

(CPUM (CM) : address 003B16)

Processor mode bits

b1 b0

0 0 : Single-chip mode

0 1:

1 0 : Not available

1 1:

Stack page selection bit

0 : 0 page

1 : 1 page

Not used (returns “1” when read)

(Do not write “0” to this bit)

Sub-clock (XCIN–XCOUT) stop bit

0 : Stopped

1 : Oscillating

Main clock (XIN–XOUT) stop bit

0 : Oscillating

1 : Stopped

Main clock division ratio selection bit

0 : f(XIN)/2 (high-speed mode)

1 : f(XIN)/8 (middle-speed mode)

Internal system clock selection bit

0 : XIN–XOUT selected (middle-/high-speed mode)

1 : XCIN–XCOUT selected (low-speed mode)

10