CD40101BMS Ver la hoja de datos (PDF) - Intersil

Número de pieza

componentes Descripción

fabricante

CD40101BMS Datasheet PDF : 8 Pages

| |||

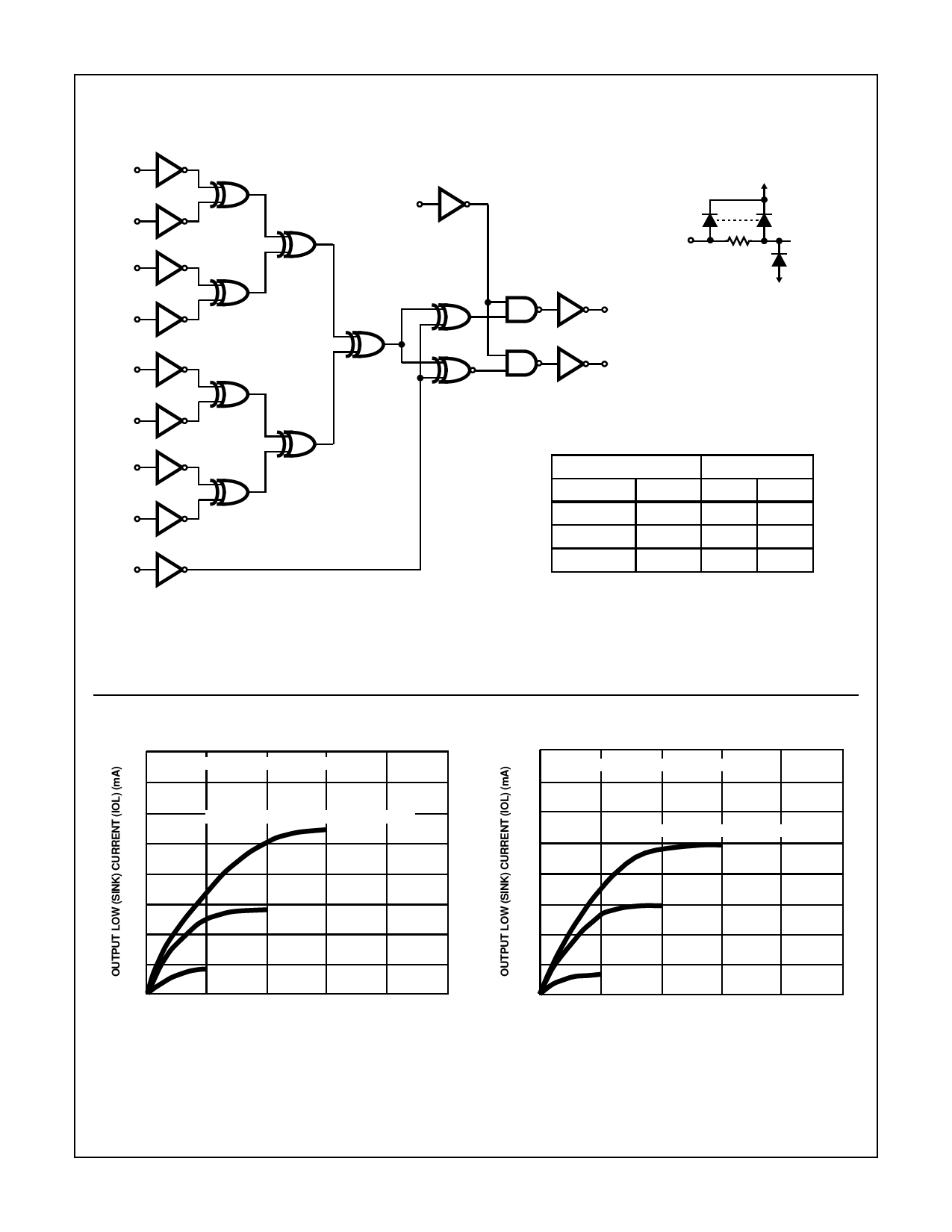

Logic Diagram

1

D1

2

D2

3

D3

4

D4

10

D5

11

D6

12

D7

13

D8

5

D9

CD40101BMS

8

INHIBIT

VDD

EVEN

OUT

9

ODD

OUT

6

VSS

* ALL INPUTS ARE PROTECTED

BY CMOS PROTECTION

NETWORK

TRUTH TABLE

INPUTS

OUTPUTS

D1-D9

INHIBIT EVEN ODD

Σ1’s = Even

0

Σ1’s = Odd

0

1

0

0

1

X

1

0

0

X = Don’t Care Logic 1 = High Logic 0 = Low

FIGURE 1.

Typical Performance Characteristics

AMBIENT TEMPERATURE (TA) = +25oC

AMBIENT TEMPERATURE (TA) = +25oC

30

GATE-TO-SOURCE VOLTAGE (VGS) = 15V

25

20

15

10V

10

5

5V

0

5

10

15

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

FIGURE 2. TYPICAL OUTPUT LOW (SINK) CURRENT CHAR-

ACTERISTICS

15.0

GATE-TO-SOURCE VOLTAGE (VGS) = 15V

12.5

10.0

10V

7.5

5.0

2.5

5V

0

5

10

15

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

FIGURE 3. MINIMUM OUTPUT LOW (SINK) CURRENT CHAR-

ACTERISTICS

7-1291