Silicon Laboratories

SI5330H-A00222-GM Datasheet - Silicon Laboratories

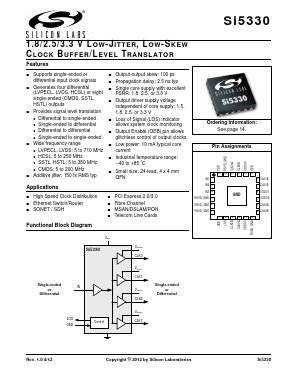

Features

■ Supports single-ended or differential input clock signals

■ Generates four differential (LVPECL, LVDS, HCSL) or eight single-ended (CMOS, SSTL, HSTL) outputs

■ Provides signal level translation

● Differential to single-ended

● Single-ended to differential

● Differential to differential

● Single-ended to single-ended

■ Wide frequency range

● LVPECL, LVDS: 5 to 710 MHz

● HCSL: 5 to 250 MHz

● SSTL, HSTL: 5 to 350 MHz

● CMOS: 5 to 200 MHz

■ Additive jitter: 150 fs RMS typ

■ Output-output skew: 100 ps

■ Propagation delay: 2.5 ns typ

■ Single core supply with excellent PSRR: 1.8, 2.5, or 3.3 V

■ Output driver supply voltage independent of core supply: 1.5, 1.8, 2.5, or 3.3 V

■ Loss of Signal (LOS) indicator allows system clock monitoring

■ Output Enable (OEB) pin allows glitchless control of output clocks

■ Low power: 10 mA typical core current

■ Industrial temperature range: –40 to +85 °C

■ Small size: 24-lead, 4 x 4 mm QFN

APPLICATIONs

■ High Speed Clock Distribution

■ Ethernet Switch/Router

■ SONET / SDH

■ PCI Express 2.0/3.0

■ Fibre Channel

■ MSAN/DSLAM/PON

■ Telecom Line Cards