Fairchild Semiconductor

SCAN18541T Datasheet - Fairchild Semiconductor

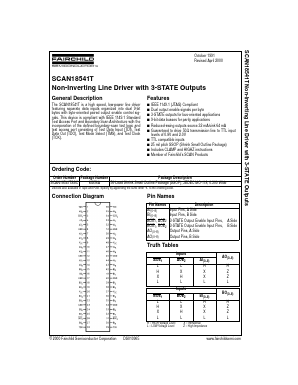

General Description

The SCAN18541T is a high speed, low-power line driver featuring separate data inputs organized into dual 9-bit bytes with byte-oriented paired output enable control signals. This device is compliant with IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI), Test Data Out (TDO), Test Mode Select (TMS), and Test Clock (TCK).

FEATUREs

■ IEEE 1149.1 (JTAG) Compliant

■ Dual output enable signals per byte

■ 3-STATE outputs for bus-oriented applications

■ 9-bit data busses for parity applications

■ Reduced-swing outputs source 32 mA/sink 64 mA

■ Guaranteed to drive 50Ω transmission line to TTL input levels of 0.8V and 2.0V

■ TTL compatible inputs

■ 25 mil pitch SSOP (Shrink Small Outline Package)

■ Includes CLAMP and HIGHZ instructions

■ Member of Fairchild’s SCAN Products