Agere -> LSI Corporation

OR2C08A-7T100 Datasheet - Agere -> LSI Corporation

Description

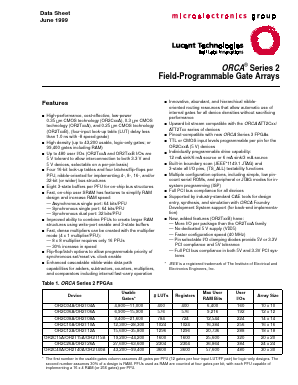

The ORCA Series 2 series of SRAM-based FPGAs are an enhanced version of the ATT2C/2T architecture. The latest ORCA series includes patented architectural enhancements that make functions faster and easier to design while conserving the use of PLCs and routing resources.

FEATUREs

■ High-performance, cost-effective, low-power 0.35 µm CMOS technology (OR2CxxA), 0.3 µm CMOS technology (OR2TxxA), and 0.25 µm CMOS technology (OR2TxxB), (four-input look-up table (LUT) delay less than 1.0 ns with -8 speed grade)

■ High density (up to 43,200 usable, logic-only gates; or 99,400 gates including RAM)

■ Up to 480 user I/Os (OR2TxxA and OR2TxxB I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis)

■ Four 16-bit look-up tables and four latches/flip-flops per PFU, nibble-oriented for implementing 4-, 8-, 16-, and/or 32-bit (or wider) bus structures

■ Eight 3-state buffers per PFU for on-chip bus structures

■ Fast, on-chip user SRAM has features to simplify RAM design and increase RAM speed:

— Asynchronous single port: 64 bits/PFU

— Synchronous single port: 64 bits/PFU

— Synchronous dual port: 32 bits/PFU

■ Improved ability to combine PFUs to create larger RAM structures using write-port enable and 3-state buffers

■ Fast, dense multipliers can be created with the multiplier mode (4 x 1 multiplier/PFU):

— 8 x 8 multiplier requires only 16 PFUs

— 30% increase in speed

■ Flip-flop/latch options to allow programmable priority of synchronous set/reset vs. clock enable

■ Enhanced cascadable nibble-wide data path capabilities for adders, subtractors, counters, multipliers, and comparators including internal fast-carry operation

■ Innovative, abundant, and hierarchical nibbleoriented routing resources that allow automatic use of internal gates for all device densities without sacrificing performance

■ Upward bit stream compatible with the ORCA ATT2Cxx/ ATT2Txx series of devices

■ Pinout-compatible with new ORCA Series 3 FPGAs

■ TTL or CMOS input levels programmable per pin for the OR2CxxA (5 V) devices

■ Individually programmable drive capability: 12 mA sink/6 mA source or 6 mA sink/3 mA source

■ Built-in boundary scan (IEEE*1149.1 JTAG) and 3-state all I/O pins, (TS_ALL) testability functions

■ Multiple configuration options, including simple, low pincount serial ROMs, and peripheral or JTAG modes for insystem programming (ISP)

■ Full PCI bus compliance for all devices

■ Supported by industry-standard CAE tools for design entry, synthesis, and simulation with ORCA Foundry Development System support (for back-end implementation)

■ New, added features (OR2TxxB) have:

— More I/O per package than the OR2TxxA family

— No dedicated 5 V supply (VDD5)

— Faster configuration speed (40 MHz)

— Pin selectable I/O clamping diodes provide 5V or 3.3V PCI compliance and 5V tolerance

— Full PCI bus compliance in both 5V and 3.3V PCI systems

* IEEE is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc.