STMicroelectronics

MK50H28DIP Datasheet - STMicroelectronics

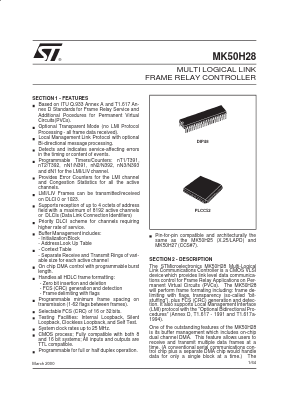

SECTION 2 - DESCRIPTION

The STMicroelectronics MK50H28 Multi-Logical Link Communications Controller is a CMOS VLSI device which provides link level data communications control for Frame Relay Applications on Permanent Virtual Circuits (PVCs). The MK50H28 will perform frame formating including: frame delimiting with flags, transparency (so-called ”bitstuffing”), plus FCS (CRC) generation and detection. It also supports Local Management Interface (LMI) protocol with the ”Optional Bidirectional Procedures” (Annex D, T1.617 - 1991 and T1.617a- 1994).

SECTION 1 - FEATURES

■ Based on ITU Q.933 Annex A and T1.617 Annex D Standards for Frame Relay Service and Additional Pocedures for Permanent Virtual Circuits(PVCs).

■ Optional Transparent Mode (no LMI Protocol Processing - all frame data received).

■ Local Management Link Protocol with optional Bi-directional message processing.

■ Detects and indicates service-affecting errors in the timing or content of events.

■ Programmable Timers/Counters: nT1/T391, nT2/T392, nN1/N391, nN2/N392, nN3/N393 and dN1 for the LMI/LIV channel.

■ Provides Error Counters for the LMI channel and Congestion Statistics for all the active channels.

■ LMI/LIV Frames can be transmitted/received on DLCI 0 or 1023.

■ Supports reception of up to 4 octets of address field with a maximum of 8192 active channels or DLCIs (Data Link Connection Identifiers)

■ Priority DLCI scheme for channels requiring higher rate of service.

■ Buffer Management includes:

- Initialization Block

- Address Look Up Table

- Context Table

- Separate Receive and Transmit Rings of variable size for each active channel

■ On chip DMA control with programmable burst length.

■ Handles all HDLC frame formatting:

- Zero bit insertion and deletion

- FCS (CRC) generation and detection

- Frame delimiting with flags

■ Programmable minimum frame spacing on transmission (1-62 flags between frames).

■ Selectable FCS (CRC) of 16 or 32 bits.

■ Testing Facilities: Internal Loopback, Silent

■ Loopback, Clockless Loopback, and Self Test.

■ System clock rates up to 25 MHz.

■ CMOS process; Fully compatible with both 8 and 16 bit systems; All inputs and outputs are TTL compatible.

■ Programmable for full or half duplex operation.

■ Pin-for-pin compatible and architecturally the same as the MK50H25 (X.25/LAPD) and MK50H27 (CCS#7).